tsmc18rf LVS res 不匹配

时间:10-02

整理:3721RD

点击:

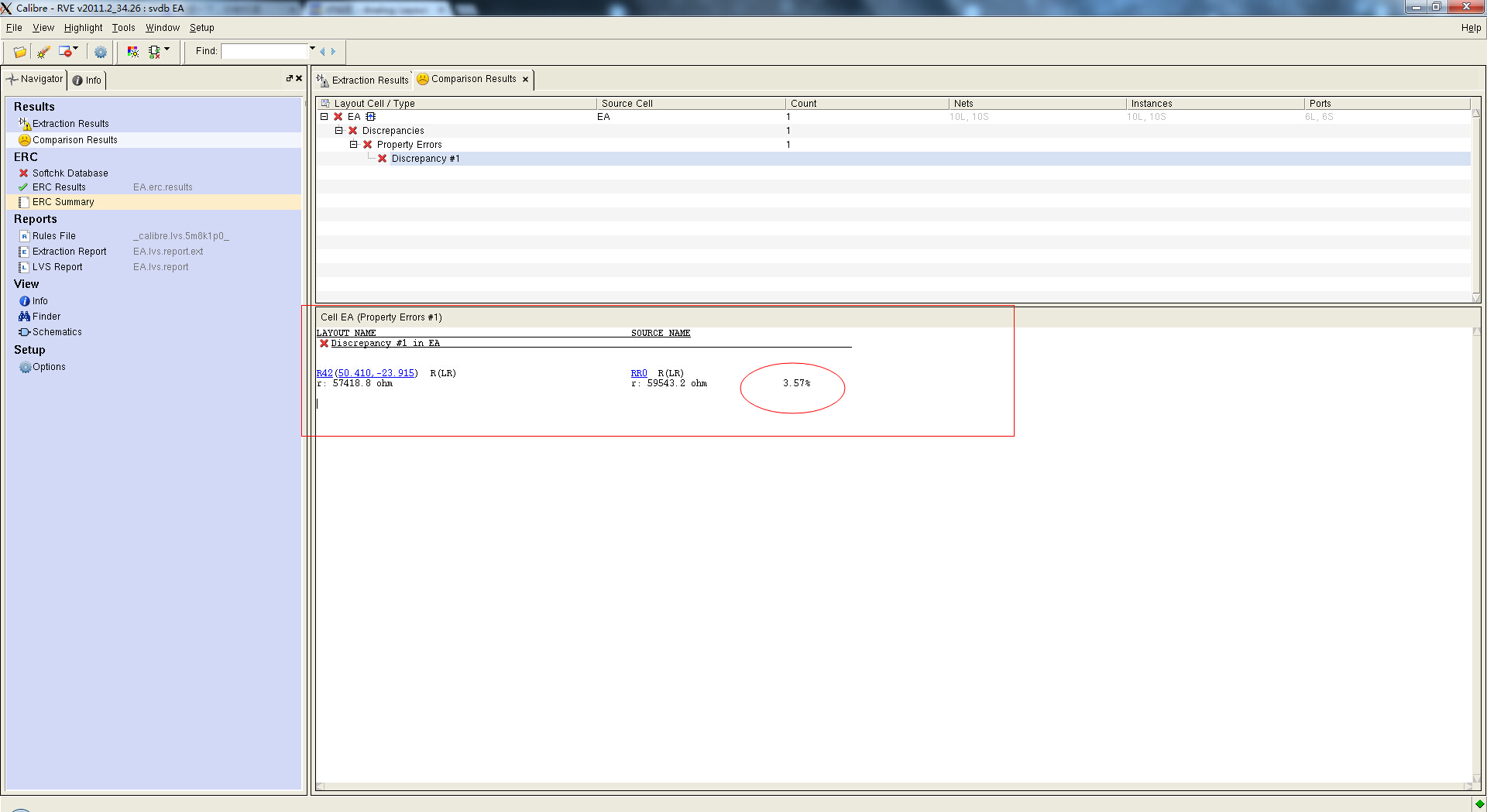

刚接触不久,一直没用这个工艺库。今天在仿LVS时发现,电阻是对比阻值。我把原理图和layout中的阻值从设定页面看是相等的。

但是仿真出来却是下面这个结果:

还请各位老师,指导下学生。

谢谢

但是仿真出来却是下面这个结果:

还请各位老师,指导下学生。

谢谢

电阻不匹配

补充下:我在版图中用的是POLY电阻,用了一圈NWELL包着的。阻值设置的一致。

我的疑问是:这是我版图的问题?还是软件设置问题?亦或对比的不是阻值而是LR?

我不是老師

看起來是對比阻值

有些誤差 3.57 %

有可能是 layout 沒畫好

LR 應該指電阻的型態

这样啊 我在电阻中间的走了一根Metal2是这个影响的吗?

有可能會變成

poly電阻 + metal2 電阻+poly電阻

或是 poly電阻 +poly電阻

看你畫的 R_symbol 而定

好像就是这样谢谢

应该和走metal2没有影响吧。觉得还是你的阻值问题。

以前遇到的这种情况,是加res dummy ,在cell top跑时,报了下面某cell中阻值对不上,一看是dummy,但是check sch和lay中是对上的,找寻后实际上是其它cell中dummy对不上,但是报到这个上面而已。

这种情况,供你参考一下。

你可以查看一下lvs run set file 文件的开关是按W&L来跑的还是按阻值来跑的,可能是这个问题引起的,