Altera PCI核调试lt_framen无法置低数据无法读写

时间:10-02

整理:3721RD

点击:

各位大神,我最近在用altera fpga芯片开发ethercat总线相关的产品,其中需用到pci接口,程序里面我是直接用的quartus 16.0软件的PCI IP核。结果测试的时候发现数据无法正确读写。

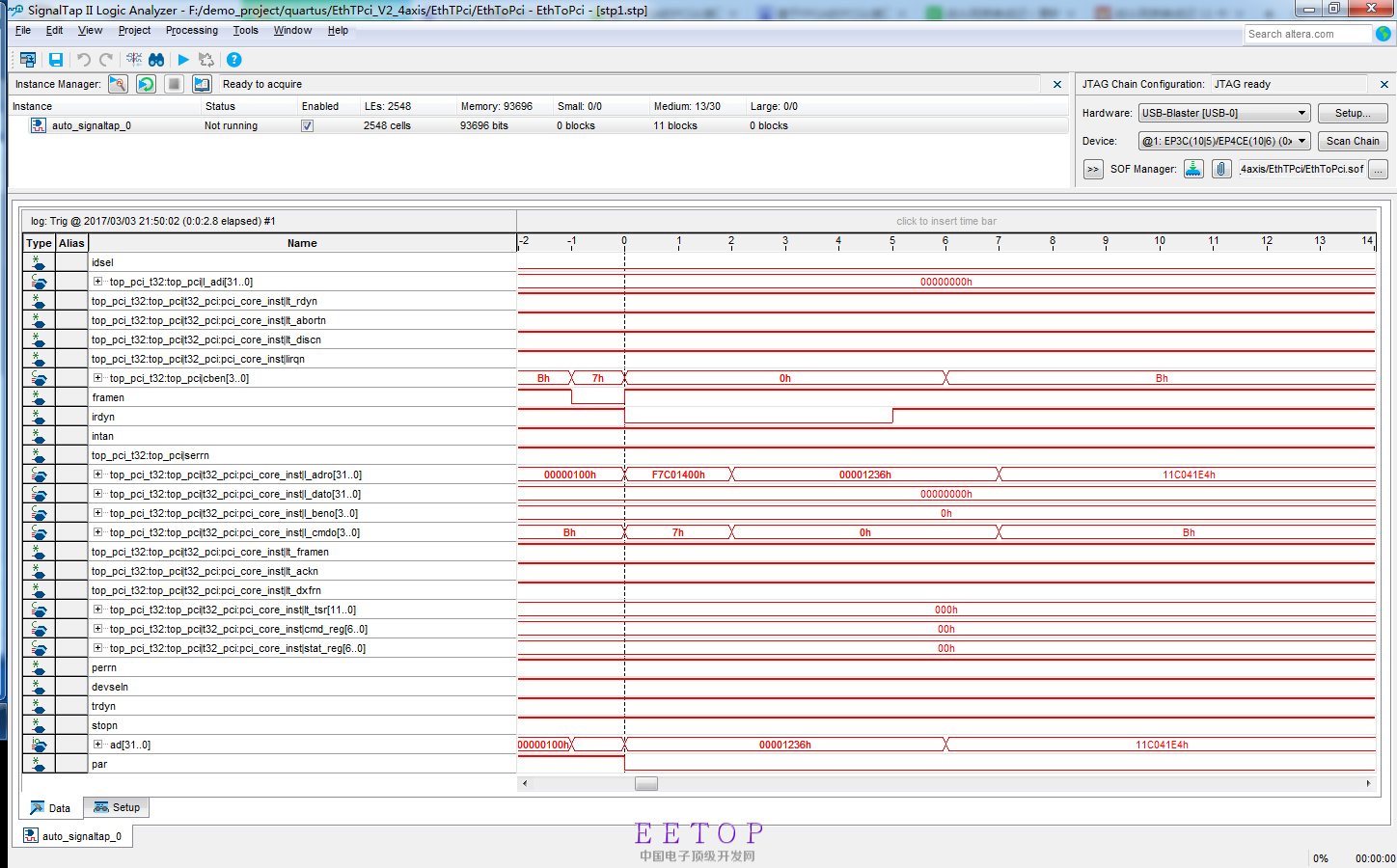

我用逻辑分析仪把PCI写过程中的相关变量都在线测试了一遍,结合PCI通信协议分析:

ad首先输入地址信号,然后framen和irdyn依次被拉低置为有效值,然后将地址信号传输到l_adro并输出,这里是正常的

接着ad输入数据信号,需要lt_framen、lt_tsr和lt_rdyn依次拉低置为有效值,但是实际测试出来的这几个信号,一直都是高电平,没有置为有效低电平,从而影响到后续的l_dato数据的传输和输出

而上述所说的lt_framen和lt_tsr都是IP核的输出变量,我好像无法对他进行相应的操作,无从下手,已经懵了好几天了,求助

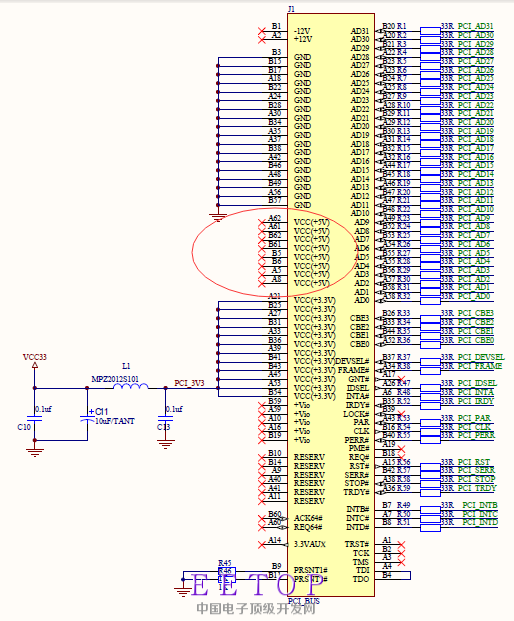

另外我查看了一下PCI接口金手指那一块的电路连接,图中A62到A8这几个5V的Vcc没有接,不知道有没有影响

被这个问题困惑好几天了,真心求助大家,我的邮箱是cth_dyx@163.com,如果有知道的请回复或者联系我,有偿也是可以的,先谢谢大家了

好东西 顶起来

这个很落伍,已经被淘汰了,十年前用过, 现在没市场。

小编搞定了吗?我最近也在弄PCI的IP核,我的现象是一进windows就死机,换一台电脑,只要对设备进行读写立马死机。

这个在工控领域领域还是有很大市场的,虽然在消费市场这个总线已经淘汰了,但是在工业控制,测控等领域这个总线还是在用,不过也在淘汰的边缘!