FPGA基础学习笔记--组合逻辑电路-多路选择器与多路分解器

时间:10-02

整理:3721RD

点击:

1.2多路选择器

1.2.1不带优先级的多路选择器

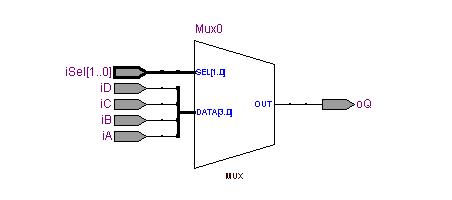

四路选择器如下

代码如下:

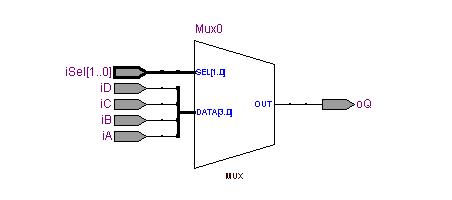

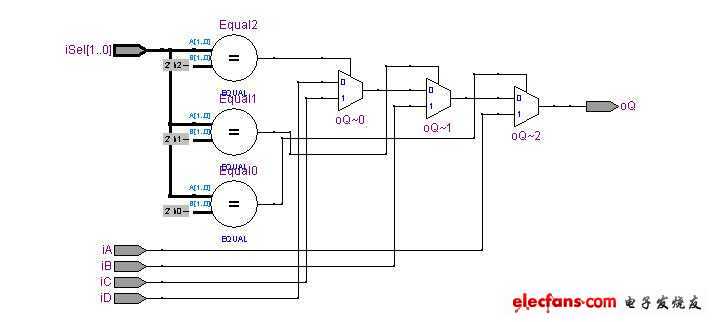

RTL级视图如下:

testbench如下:

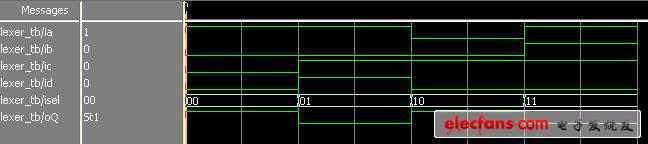

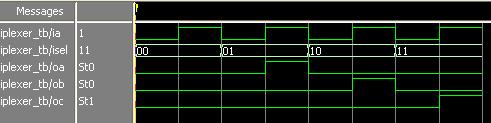

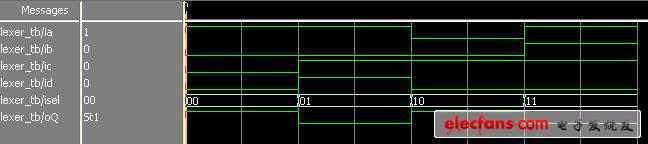

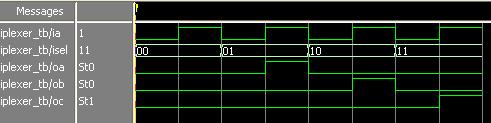

RTL级仿真图形如下:

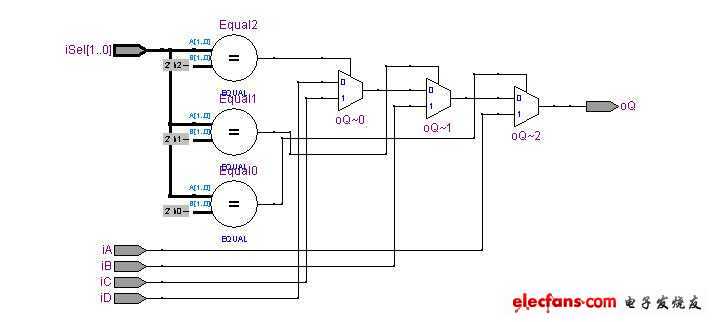

1.2.2 带优先级的多路选择器

代码如下:

1.2.3多路分解器

一路输入,三路输出分解器代码如下:

1.2.1不带优先级的多路选择器

四路选择器如下

代码如下:

- module multiplexer

- (

- input iA,

- input iB,

- input iC,

- input iD,

- input [1:0] iSel,

- output reg oQ

- );

-

- always @(*)

- begin

- case(iSel)

- 2'b00 : oQ=iA;

- 2'b01 : oQ=iB;

- 2'b10 : oQ=iC;

- 2'b11 : oQ=iD;

- endcase

- end

-

- endmodule

RTL级视图如下:

testbench如下:

- `timescale 1 ns/ 1 ns

- module logics_tb();

-

- reg ia;

- reg ib;

-

- wire oAnd;

- wire oOr;

- wire oNot;

-

- initial

- begin

- ia=0;

- #40 ia=1;

- #40 ia=0;

- #40 ia=1;

- #40 ia=0;

- end

-

- initial

- begin

- ib=0;

- #40 ib=0;

- #40 ib=1;

- #40 ib=1;

- #40 ib=0;

- end

-

- logics logics_inst

- (

- .iA(ia),

- .iB(ib),

- .oAnd(oAnd),

- .oOr(oOr),

- .oNot(oNot)

- );

-

- endmodule

RTL级仿真图形如下:

1.2.2 带优先级的多路选择器

代码如下:

- module multiplexer

- (

- input iA,

- input iB,

- input iC,

- input iD,

- input [1:0] iSel,

- output reg oQ

- );

-

- always @(*)

- if(iSel==2'b00)

- oQ=iA;

- else if(iSel==2'b01)

- oQ=iB;

- else if(iSel==2'b10)

- oQ=iC;

- else

- oQ=iD;

-

- endmodule

1.2.3多路分解器

一路输入,三路输出分解器代码如下:

- module de_multiplexer

- (

- input iA,

- input [1:0] iSel,

- output reg oA,

- output reg oB,

- output reg oC

- );

-

- always @(*)

- begin

- oA=0;oB=0;oC=0;

- case(iSel)

- 2'b00 : oA=iA;

- 2'b01 : oB=iA;

- 2'b10 : oC=iA;

- default :;

- endcase

- end

-

- endmodule

- `timescale 1ns/1ns

- module de_multiplexer_tb;

- reg ia;

- reg [1:0] isel;

- wire oa;

- wire ob;

- wire oc;

-

- initial

- begin

- ia=0;

- forever

- #10 ia=~ia;

- end

-

- initial

- begin

- isel=2'b00;

- #20 isel=2'b01;

- #20 isel=2'b10;

- #20 isel=2'b11;

- #20 $stop;

- end

-

- de_multiplexer de_multiplexer_inst

- (

- .iA(ia),

- .iSel(isel),

- .oA(oa),

- .oB(ob),

- .oC(oc)

- );

-

- endmodule

学习了

受益了

顶顶顶顶顶顶顶顶顶顶顶顶顶顶顶顶顶顶顶顶顶顶顶顶顶

小编太厉害,引得我们无不称羡啊,32个赞

不错啊!不错啊!不错啊!