FPGA Verilog HDL 设计实例系列连载------交通灯的控制

时间:10-02

整理:3721RD

点击:

原理与要求:

在十字路口,每条道路各有一组红、黄、绿灯和倒计时显示器,用以指挥车辆和行人有序的通行。其中。红灯亮表示该道路禁止通行;黄灯亮表示停车;绿灯亮表示可以通行;倒计时显示器是用来显示允许通行或禁止通行的时间。交通灯控制器就是用于自动控制十字路口的交通灯和计时器,指挥各种车辆和行人安全通过。

下面我们就设计一个这样的:

1)、在十字路口设置一组红、黄、绿等,显示顺序为:红,绿,黄,红……

2)、设置一组数码管,以倒计时的方式显示允许通过或禁止通过的时间,其中绿灯、黄灯、红灯的持续时间为20s,5s,25s。

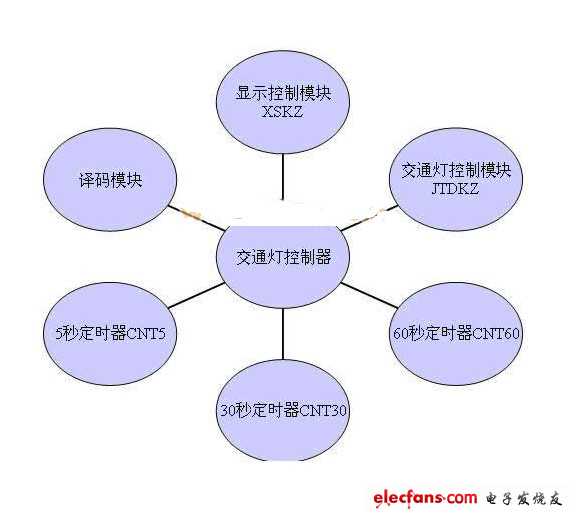

Verilog HDL实现

设计文件输入Verilog HDL代码。

系统分为两个模块,一个是顶层traffic,一个是分频模块clkgen。

分频模块clkgen的实现如下:

- //-------------------------------------------------------------------------------------------------

- //

- // File : clkgen.v

- // Generated : 2011-07-24

- // Author : wangliang

- //

- //-------------------------------------------------------------------------------------------------

- `timescale 1 ns / 1 ps

-

- module clkgen ( rst ,clkout ,clk );

-

- input rst ;

- wire rst ;

- input clk ;

- wire clk ;

-

- output clkout ;

- reg clkout ;

-

- reg [31:0] count1;

-

- always @ ( posedge clk or negedge rst)

-

- begin

- if ( rst== 1'b0 ) begin

- clkout = 32'd25000000) begin

- clkout 1'b1 )

- if ( num [3:0] == 0 ) begin

- num [ 3:0 ] <= 4'b1001;

- num [7:4] <= num [7:4] -1 ;

- end

- else num [3:0] <= num [3:0] -1 ;

- if ( num == 2 )

- temp <= 0 ;

- end

- end

- else begin

- lamp <= 3'b100 ;

- state <= red ;

- temp <= 0 ;

- end

- end

- end

-

-

- /************************ 数码管译码**************************************/

- reg [7:0] Y_r_1;

- reg [7:0] Y_r_2;

-

- assign seven_seg[7:0] ={1'b1,(~Y_r_1[6:0])};

- assign seven_seg[15:8] = {1'b1,(~Y_r_2[6:0])};

-

- always @(num[3:0] )

- begin

- Y_r_1 = 7'b1111111;

- case (num[3:0] )

- 4'b0000: Y_r_1 = 7'b0111111; // 0

- 4'b0001: Y_r_1 = 7'b0000110; // 1

- 4'b0010: Y_r_1 = 7'b1011011; // 2

- 4'b0011: Y_r_1 = 7'b1001111; // 3

- 4'b0100: Y_r_1 = 7'b1100110; // 4

- 4'b0101: Y_r_1 = 7'b1101101; // 5

- 4'b0110: Y_r_1 = 7'b1111101; // 6

- 4'b0111: Y_r_1 = 7'b0000111; // 7

- 4'b1000: Y_r_1 = 7'b1111111; // 8

- 4'b1001: Y_r_1 = 7'b1101111; // 9

- 4'b1010: Y_r_1 = 7'b1110111; // A

- 4'b1011: Y_r_1 = 7'b1111100; // b

- 4'b1100: Y_r_1 = 7'b0111001; // c

- 4'b1101: Y_r_1 = 7'b1011110; // d

- 4'b1110: Y_r_1 = 7'b1111001; // E

- 4'b1111: Y_r_1 = 7'b1110001; // F

- default: Y_r_1 = 7'b0000000;

- endcase

- end

-

- always @( num[7:4] )

- begin

- Y_r_2 = 7'b1111111;

- case ( num[7:4] )

- 4'b0000: Y_r_2 = 7'b0111111; // 0

- 4'b0001: Y_r_2 = 7'b0000110; // 1

- 4'b0010: Y_r_2 = 7'b1011011; // 2

- 4'b0011: Y_r_2 = 7'b1001111; // 3

- 4'b0100: Y_r_2 = 7'b1100110; // 4

- 4'b0101: Y_r_2 = 7'b1101101; // 5

- 4'b0110: Y_r_2 = 7'b1111101; // 6

- 4'b0111: Y_r_2 = 7'b0000111; // 7

- 4'b1000: Y_r_2 = 7'b1111111; // 8

- 4'b1001: Y_r_2 = 7'b1101111; // 9

- 4'b1010: Y_r_2 = 7'b1110111; // A

- 4'b1011: Y_r_2 = 7'b1111100; // b

- 4'b1100: Y_r_2 = 7'b0111001; // c

- 4'b1101: Y_r_2 = 7'b1011110; // d

- 4'b1110: Y_r_2 = 7'b1111001; // E

- 4'b1111: Y_r_2 = 7'b1110001; // F

- default: Y_r_2 = 7'b0000000;

- endcase

- end

- endmodule

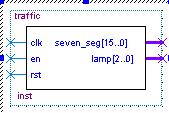

图1.1 分频模块

图1.2 顶层模块

图1.2实例化图1.1,所以只需要对图1.2上的引脚进行分配。其中,clk接50MHZ系统时钟,rst接复位信号,en接按键,控制开始与结束,lamp[2..0]接红黄绿灯,seven_seg[15..0]接2个数码管。实验结果:

红灯倒计时25S,转绿灯20S,转黄灯5S,转红灯25S。PS:有想法的可以再尝试着做个十字路的那种红绿灯哦。

学习了。谢谢

路过,看看

不错哦

功能有点简单啊,可以再升华一下。

学习下,谢谢小编了

多谢分享。

谢谢小编分享

谢谢小编

好东西,真是各种大牛啊

学习

收益匪浅啊,谢谢

实例很好,很感谢小编

小编好人