Verilog并行数据处理问题

时间:10-02

整理:3721RD

点击:

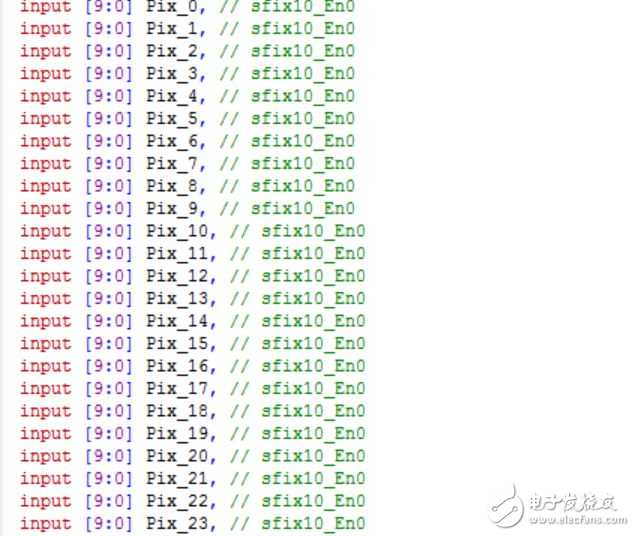

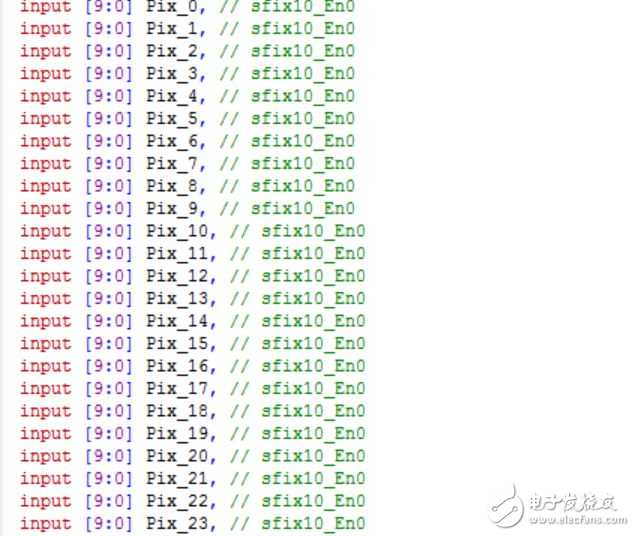

我在一个小练习中需要处理图像数据,一帧的图像是并行进来的,如下图所示:

一帧总共有几千个pixel。假设说我想给每一个pixel乘上一个不同的系数(使用乘法器实现),乘法器是流水线结构。请问有没有简洁的Verilog语言(当然也要是可综合的)能让我用较少的乘法器实现(比如说,我有没有可能在一个循环中遍历这些输入信号)。乘法器用的太多,且不说实际电路面积太大的问题(假设我不是很care delay),首先代码就是很臃肿很长,都是相似的模块,但这些pixel数据是并行进来的,又不是存在一个ram中,不知如何能循环遍历,希望各位大佬不吝赐教,谢谢!

一帧总共有几千个pixel。假设说我想给每一个pixel乘上一个不同的系数(使用乘法器实现),乘法器是流水线结构。请问有没有简洁的Verilog语言(当然也要是可综合的)能让我用较少的乘法器实现(比如说,我有没有可能在一个循环中遍历这些输入信号)。乘法器用的太多,且不说实际电路面积太大的问题(假设我不是很care delay),首先代码就是很臃肿很长,都是相似的模块,但这些pixel数据是并行进来的,又不是存在一个ram中,不知如何能循环遍历,希望各位大佬不吝赐教,谢谢!