Xilinx程序下载方式

时间:10-02

整理:3721RD

点击:

这几天一直对FPGA的程序下载方式感到疑惑,特别是关于SPI的下载以及多个芯片的程序下载控制。先说说单片下载问题。以Xilinx的下载方式为例,通常我们做实验、自己学习的时候都是以JTAG模式下载到开发板上的FPGA芯片中,也就是说JTAG是我们最熟悉的通常说的嵌入式下载模式(当前流行的STM32系列单片机的烧写也是这种主要模式),但是稍微熟悉点的人都知道JTAG只是一种在线调试下载模式,也就是说是实时可以改变的,JTAG只是程序的一个传输介质,只在上电后才能正常工作,并不会在芯片中保存下程序,即程序不能固化到开发板上的芯片中,掉电后程序就失去。为了解决掉电后程序丢失的问题,不同的FPGA设计生产商都有自己的解决方法,以xilinx的FPGA芯片为例,就是将程序代码转化成固化烧写到一个外挂的Flash中,本人接触的较多的是通过iMPACT软件进行一定得配置将.bit文件转化成.mcs文件(具体可以查阅xilinx的相关教程),然后再下载到开发板上的flash中。这整个过程都没问题,但是本人一直很奇怪.mcs文件是怎么写入flash中的,是通过JTAG连接器经过FPGA芯片在写入flash中的?还是直接通过JTAG下载到flash中的?通过网上相关论坛查询并没有找到自己想要的相关答案,讲的大多是altera的三种下载配置方式,但是本人并不太理解,或者说不是我想要的答案。

通过查阅xilinx芯片开发板的相关文件后基本算是解决了这个问题。在FPGA Configuration User Guide和Configuring FPGAs from SPI Serial Flash两个文档中有详细的关于flash下载的配置说明。通过阅读文档知道xilinx主要是JTAG在线调试和SPI Serial Flash两种模式,而SPI Serial Flash包含三种:Third-party programmers (off-board programming)、Indirect in-system programming (JTAG tool vendor or custom solution)和Direct in-system programming (SPI direct interface connect)。在此本人理解是,通过JTAG连接器将程序固化到flash中的是第二种间接模式,但是查看原理图发现flash芯片M25P16并没有直接与JTAG相连的引脚都是连接到FPGA芯片引脚(如图1),文档中也没有作具体解释,故本人认为这种间接模式是通过JTAG将.mcs文件通过FPGA后再传到flash中保存的。

图1 M25P16

对于直接进行SPI模式下载的配置,如图2,以Virtex-5 FPGA的配置为例。图中左边是JTAG在线调试模式,右边是恒忆的M25PXX系列flash芯片,flash芯片和FPGA相关引脚互联,通过类似JTAG接口对通常的SPI四线进行相应的控制输入,既是直接将程序下载到外部flash中,掉电重新上电后程序不会丢失,即可启动。但是这要注意主从配置问题。

图2

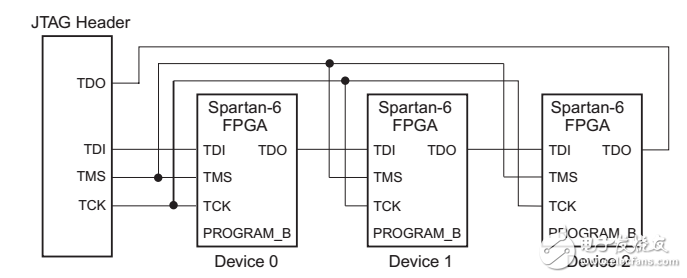

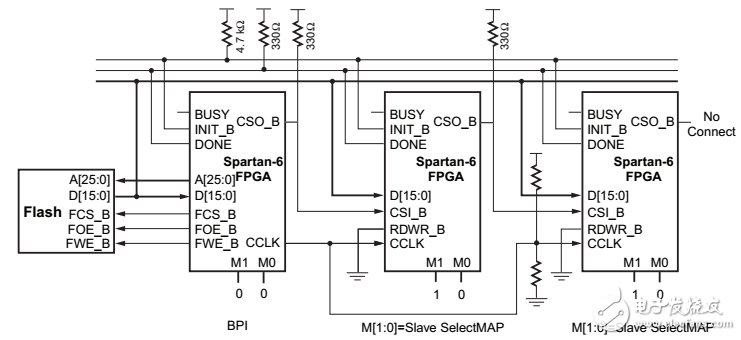

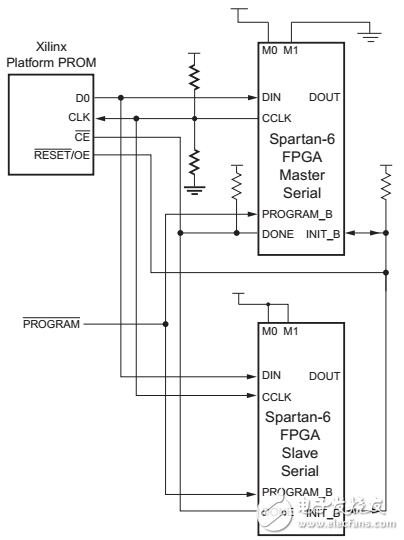

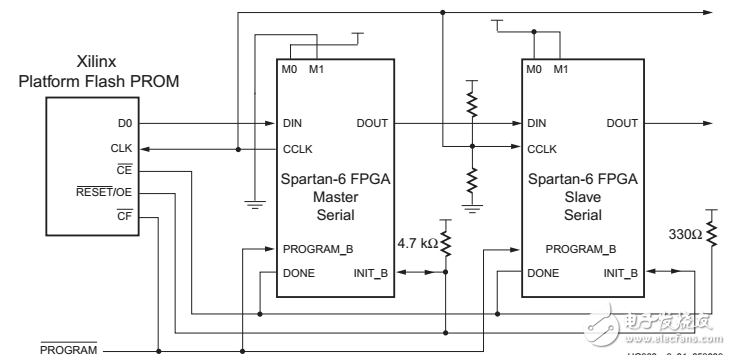

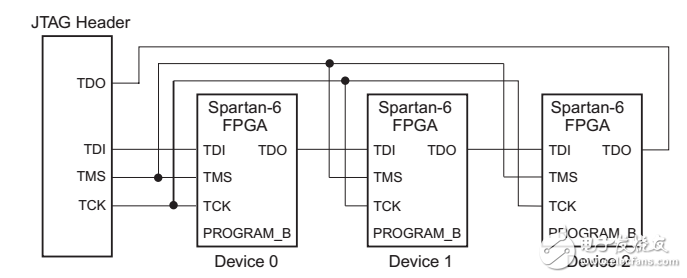

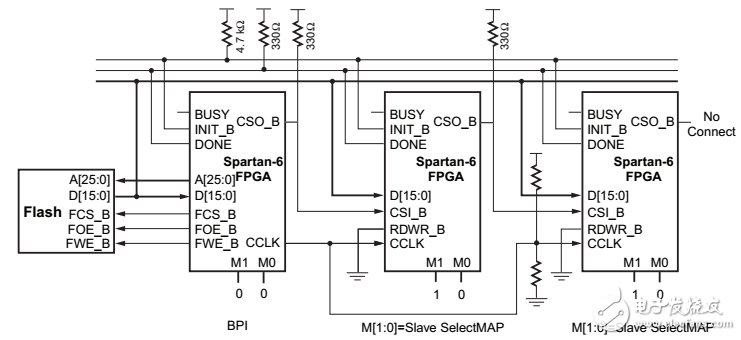

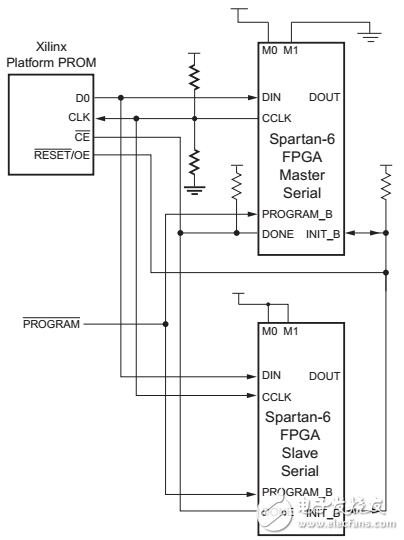

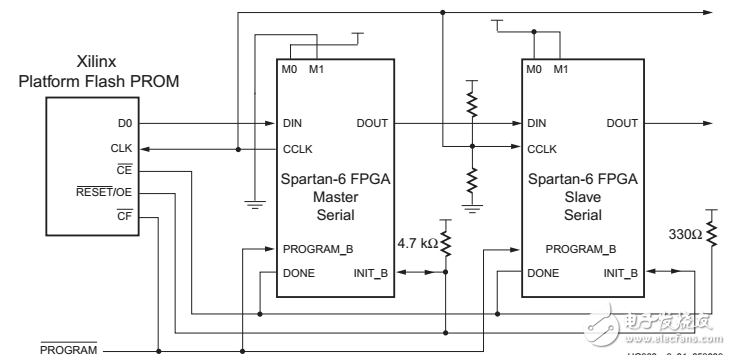

现在来说说多芯片控制问题。多芯片中和单芯片一样,下载方式也是上面几种。直接用图说明。

图3 JTAG多芯片模式

图4 并行flash多芯片

图5 串行主从多芯片

图6 FPGA 主从模式以上仅是本人的一定理解,如有不对,欢迎大交流指正。

通过查阅xilinx芯片开发板的相关文件后基本算是解决了这个问题。在FPGA Configuration User Guide和Configuring FPGAs from SPI Serial Flash两个文档中有详细的关于flash下载的配置说明。通过阅读文档知道xilinx主要是JTAG在线调试和SPI Serial Flash两种模式,而SPI Serial Flash包含三种:Third-party programmers (off-board programming)、Indirect in-system programming (JTAG tool vendor or custom solution)和Direct in-system programming (SPI direct interface connect)。在此本人理解是,通过JTAG连接器将程序固化到flash中的是第二种间接模式,但是查看原理图发现flash芯片M25P16并没有直接与JTAG相连的引脚都是连接到FPGA芯片引脚(如图1),文档中也没有作具体解释,故本人认为这种间接模式是通过JTAG将.mcs文件通过FPGA后再传到flash中保存的。

图1 M25P16

对于直接进行SPI模式下载的配置,如图2,以Virtex-5 FPGA的配置为例。图中左边是JTAG在线调试模式,右边是恒忆的M25PXX系列flash芯片,flash芯片和FPGA相关引脚互联,通过类似JTAG接口对通常的SPI四线进行相应的控制输入,既是直接将程序下载到外部flash中,掉电重新上电后程序不会丢失,即可启动。但是这要注意主从配置问题。

图2

现在来说说多芯片控制问题。多芯片中和单芯片一样,下载方式也是上面几种。直接用图说明。

图3 JTAG多芯片模式

图4 并行flash多芯片

图5 串行主从多芯片

图6 FPGA 主从模式以上仅是本人的一定理解,如有不对,欢迎大交流指正。

小编功法很棒,长见识