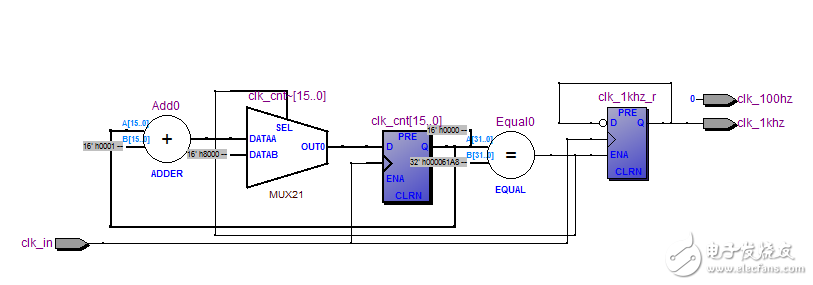

对50MHZ时钟分频,输出1KHZ时钟信号和100HZ时钟信号

时间:10-02

整理:3721RD

点击:

上图是RTL电路图,为什么输出信号100hz的信号左侧什么也没有接呢?求大神指点。如果有错,应该怎么改。

程序如下:

module paobiao_fenpin(clk_in,clk_100hz,clk_1khz);//clk_ms表示100HZ时钟用于计数,clk_khz表示1KHZ时钟用于数码管扫描;

input clk_in;//50M晶振

output clk_100hz;//百分秒;

output clk_1khz;

wire clk_100hz;

wire clk_1khz;

reg clk_100hz_r;

reg clk_1khz_r;

reg [1:0]clk_100hz_cnt;

reg [15:0]clk_cnt;

initial clk_1khz_r=1;

initial clk_cnt=1;

always@(posedge clk_in)//1KHZ时钟计数;

begin

if(clk_cnt==25000)

begin

clk_cnt<=1;

clk_1khz_r<=~clk_1khz_r;

end

else

begin

clk_cnt<=clk_cnt+1'b1;

end

end

assign clk_1khz=clk_1khz_r;//输出1KHZ时钟

always@(posedge clk_1khz_r)

begin

if(clk_100hz_cnt==5)

begin

clk_100hz_cnt<=0;

clk_100hz_r<=~clk_100hz_r;

end

else

begin

clk_100hz_cnt<=clk_100hz_cnt+1'b1;

end

end

assign clk_100hz=clk_100hz_r;

endmodule

别的不说,为什么要加入initial语句?这个clk_100hz_cnt怎么不初始化?

把50MHZ晶振同时分频成1khz 和100hz 上面这种方法行吗 可以把1khz上升沿作为100hz信号计数的触发信号吗 边沿直接posedge clk_1khz这样写对吗 这是我的疑问 能帮我解答一下吗

initial是不对 100hz这个 不初始化不是默认为1吗

理论上,你的想法是可以的,在产生100hz时,为什么不是根据clk_in时钟来产生?还有,你为什么不用PLL来产生时钟信号?这样产生的时钟好多了

第二个时钟问题,用输入clkin产生100hz时钟

已经有1khz了 再从头计数产生100hz不是重复了一部分吗 而且浪费资源呀 对1khz占用的资源比较少 pll的话我还没想过 我这是做数字跑表的分频模块 要1khz个100hz时钟后面用

这样不就浪费了1khz的资源了吗 还得从头计数

reg [1:0]clk_100hz_cnt; 太小了

无法满足if(clk_100hz_cnt==5) 这个条件 无法驱动 clk_100hz_r 这个寄存器 默认为0

对呀 万分感谢

reg [1:0]clk_100hz_cnt;不对

谢谢 已经解决了 这个太小了 改了这个clk_100hz_cnt就行了