如何理解Xilinx的RTL图

时间:10-02

整理:3721RD

点击:

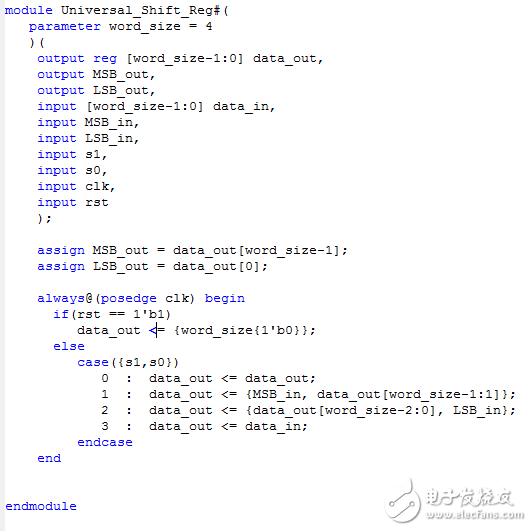

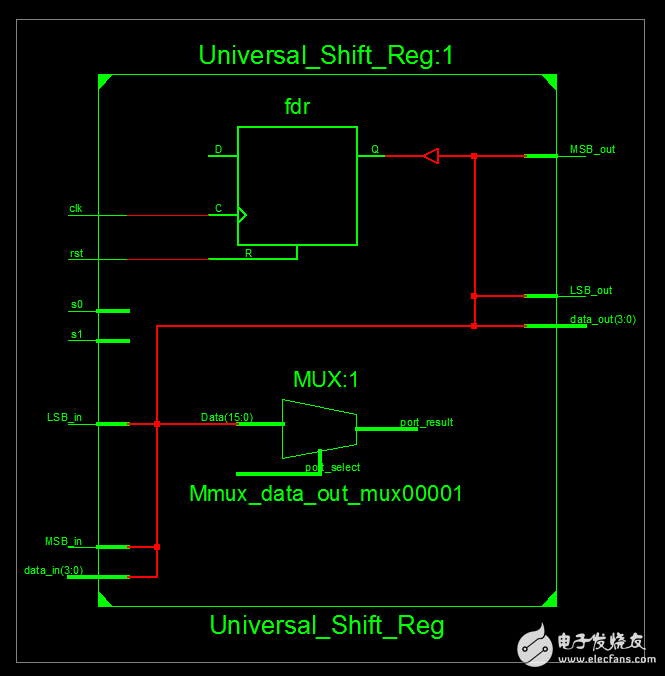

各位大神,我的通用移位寄存器HDL代码如上,我用的Xilinx ISE开发环境,我想问综合后的RTL图要如何理解,上述HDL代码的RTL图如下所示,

请问图中那些未连接的pin都是什么情况?该图要如何与HDL代码联系起来?

1.结合你的代码啊 ,比如你s0,s1就是你代码中的input s1,input s0

2.fdr,一看就是一个D边沿触发器,这数字电路就有啊

3.应该是buffer吧,看对应器件类型的 Libraries Guide for Schematic Designs文件啊,官网有下载的

4.这你就得看你对HDL转化为实际电路了,就那个always语句:是个上升沿触发的时序逻辑电路,其中包括2位选择器(case语句)。assign代表连续赋值,你可以看成一条连线,连接在一起。

大神们,你们在哪儿?

未连接的pin不代表实际没连接起来

1.那要如何看这种RTL图呢?那些没连接的pin我怎么知道它的意义?

2.那些元件,比如fdr我要从哪些资料里看他的功能呢?

3.有的RTL图中的连线上会有红色的小三角,那是什么意思?

4.拿到一个很大的HDL代码,还没注释,要从何看起呢?

麻烦您帮我解惑!

有些未连接的可能是定义了但是没有使用吧

小三角形是因为是这根线左右的数据位数不等

确实定义了,也使用了。

谢谢您!不过Libraries Guide for Schematic Designs我看过,有的元件里边是没有的呀,这个例子比较简单,但是综合一些大型的模型,RTL里会出现一些那个文档里没有的元件,所以我也很郁闷。

另外就比如这个例子,fdr是一个D触发器,那么为什么输入管脚没有接线呢?我的代码里连上的,而且仿真是可以过的。

能具体一点儿吗?LSB_out 和data_out(3:0)也位数不等,为什么没有小三角?

另外在别的工程的RTL里我发现小三角的方向有不同的,那不同的方向又有什么意义呢?