例化相同的模块

好像可以用python写个脚本,不过我也不会,坐等高手

1. 据我所示,没法用循环的。

2. 可以用C、perl等,打印出相应的verilog代码,再贴回去。

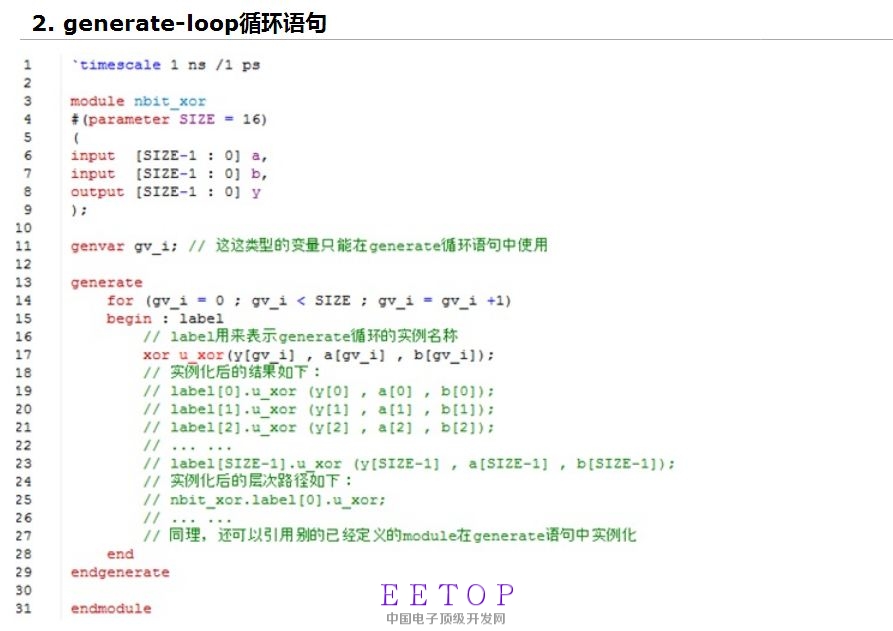

使用generate(genvar,label)

#转自,http://www.cnblogs.com/fbi888/archive/2013/11/27/3445178.html

generate_loop

可以用for语句产生啊,for就是用来干这些循环的事情。

只是要注意一点的是端口信号不能增量命名,但是可以通过把信号定义成 wire [data_width-1:0] signals [63:0] 这样的形式。

忘了还有一点是模块命名,可以直接用 {string, i} 这种形式进行字符连接。

还是举个例子吧,这个我也没试过,不知道能不能综合。

- wire [data_width-1:0] data_in [63:0] ;wire [data_width-1:0] data_out [63:0] ;

- for(i=0; i<64, i++) begin

- basemodule {“basemodule_inst”,i}

- (

- .din (data_in[64*i]),

- .dout (data_out[64*i]),

- );

- end

parameter SIZE = 5;

input [SIZE-1 : 0] sig;

input [SIZE-1 : 0] sig_in;

output [SIZE-1 : 0] sig_o;

genvar i

generate

for (i=0;i<SIZE;i=i+1)

begin: TAG

module_test inst_ (.a(sig),.b(sig_in),.c(sig_o));

end

endgenerate

漏了变量

module_test inst_ (.a(sig\[i\]),.b(sig_in\[i\]),.c(sig_o\[i\]));

这种循环生成,反而会产生问题

刚刚去实践了下,用generate for可以综合

两种办法,generate 或者实例数组,看情况使用

学习了