Xilinx FPGA开发板存储器的最大带宽怎么计算

时间:10-02

整理:3721RD

点击:

PC上,DDR最大頻帶=外頻x2x8BYTES。依系統不同,看你的記憶體總共位元數。如果你只用一顆x8的IC,那就是 1200M x 2 x 1 = 2.4G。如果有32位元,那就可以到 9.6G。

理論上是如此,這只是在連續READ或WRITE下才能達到。因為DDR需要下command才能動作,這都會浪費一些時間。

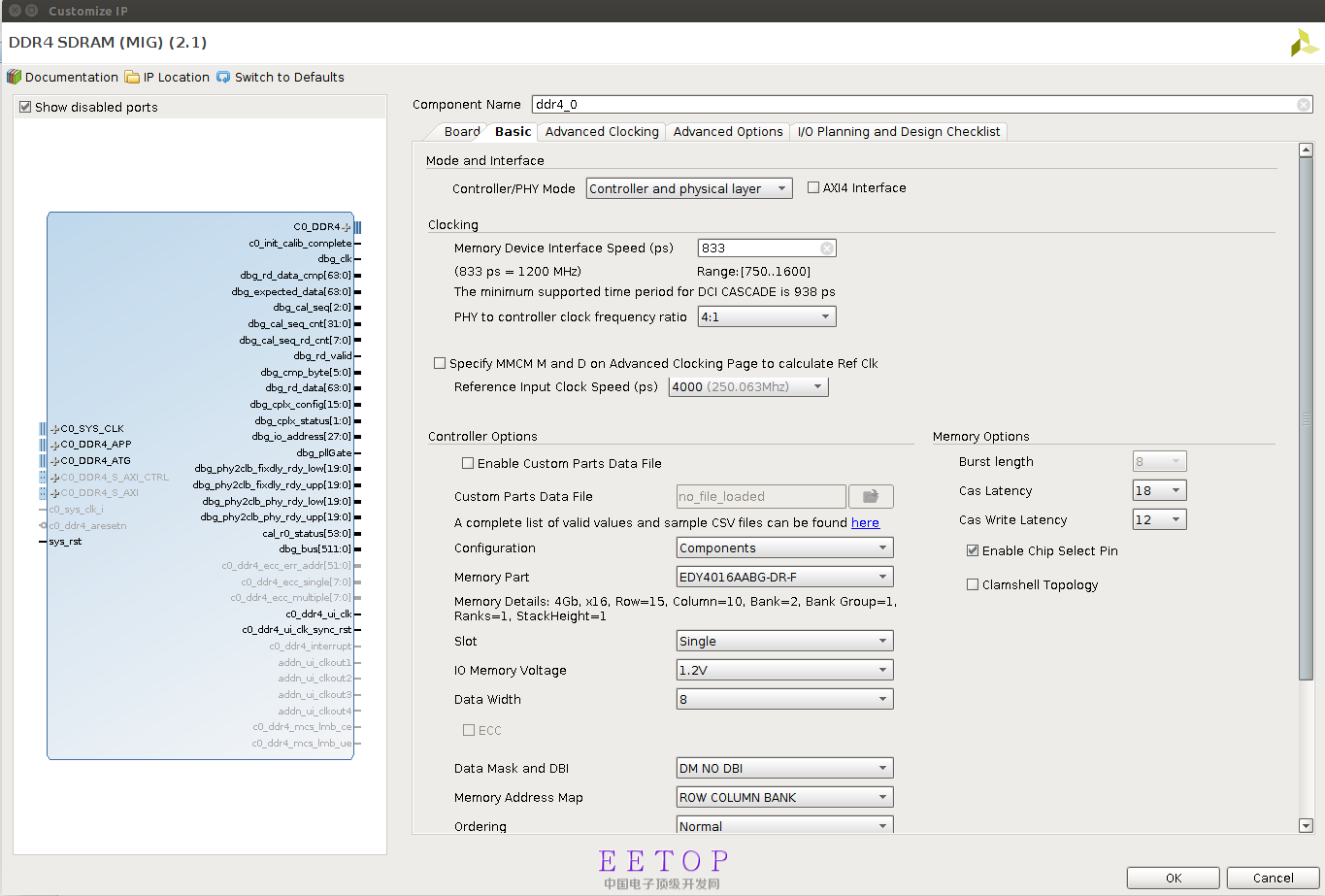

谢谢您的回答, 在设置MIG IP的时候,我对 PHY to controller clock frequency ratio 这个参数不明白, 我在想最后的结果是否与这个有关系?或者说,我想知道的是这个参数什么作用?因为我看到它后面的下拉菜单里面就这个 4:1选项,没有其他的. 另外,我在本站看到一个介绍ddr3 MIG IP设置的帖子地址是http://bbs.eetop.cn/viewthread.php?tid=577122,在附件第34页中看到如下图所示,没有理解和这里对应部分的那句话——“你待会儿操作。因为你这里选了4:1” 。ddr3这里的配置和ddr4的配置两个是一样的吗?

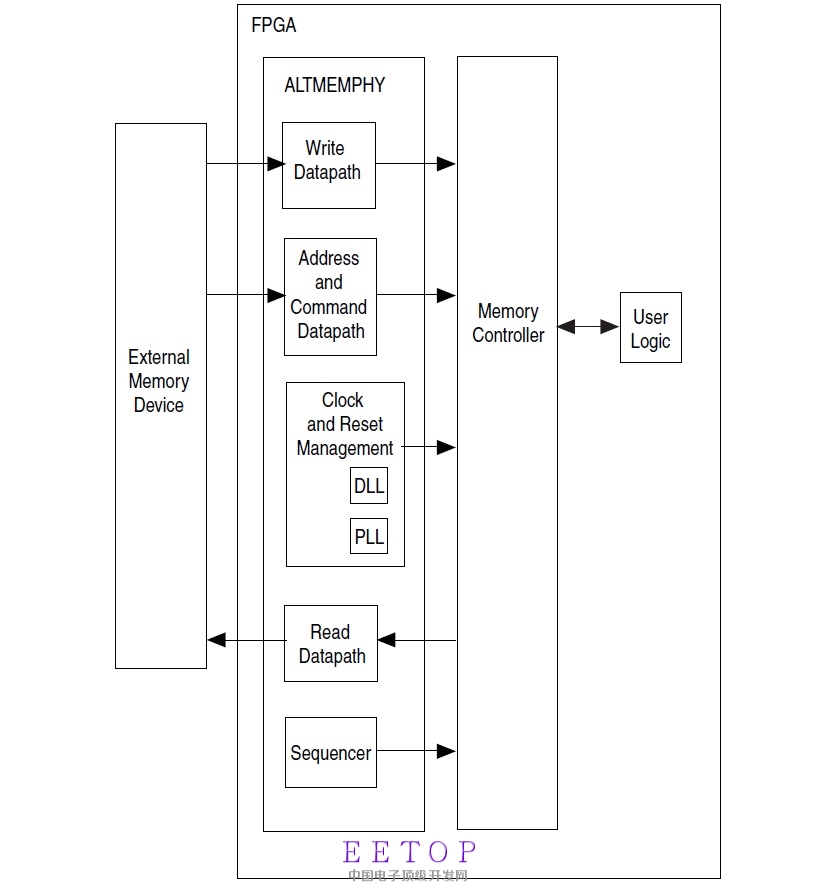

我比較懂的是Altera的IP,如圖

應該是與圖中 PHY內的clock相同,是提供給設計的 memory controller 用,以便與 PHY 同步。

不好意思,刚回复你, 谢谢,我现在感觉有些明了了 最大带宽应该就是 1200M * 2 * 80 / 8 = 2400MBps