两个时钟clka,clkb,通过sel信号2选1。处理方法探讨。

时间:10-02

整理:3721RD

点击:

下面这段设计方法是业界标准的设计方法么? 我的问题是: 既然sel信号对于clka和clkb来说都是异步信号,为什么不用打两拍的方式来去除亚稳态? 如果打两拍同步后,分别变成了sel_clka和sel_clkb后,下面这段分析,以及波形图,还正确么/

请问,业界标准的做法是什么?

在《华为_大规模逻辑设计指导书.pdf》中提到,

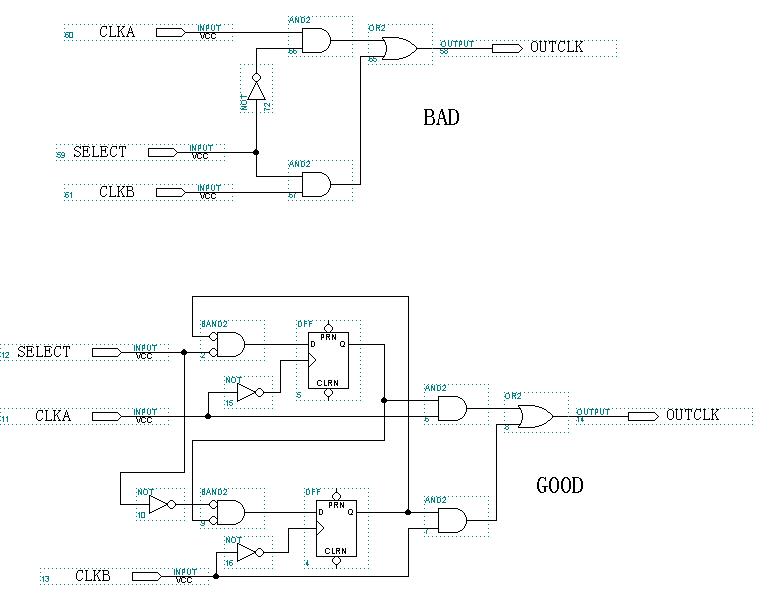

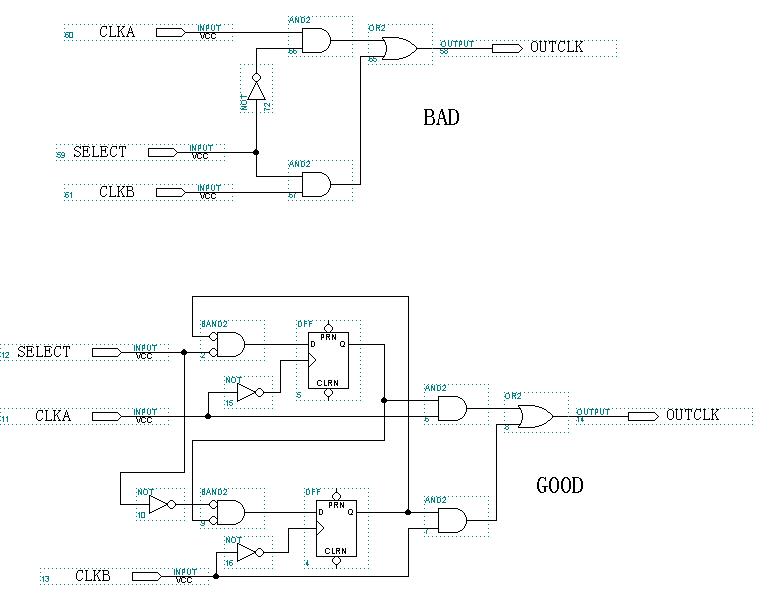

通过组合逻辑对触发器的时钟在多个时钟中选择一个如下图所示:

上图中标为BAD的一个由于直接用组合逻辑实现在CLKA CLKB两个时钟中二选一的功能,而组合电路由于不同路径的延迟不同,所以在电路的时钟输出很容易产生毛刺。而标为GOOD 的一个由于对选择信号SELECT分别用两个触发器进行了同步化所以在时钟的输出端不会产生毛刺。

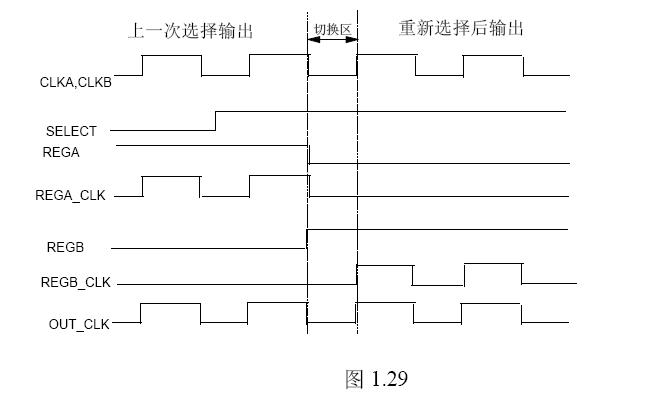

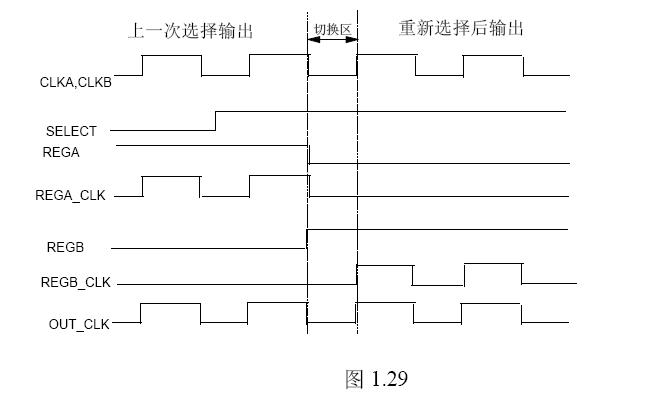

图1.29是图1.28中GOOD电路的原理时序图。其中REGA表示接CLKA的触发器,其对应的与门输出为REGA_CLK, 同样定义REGB和REGB_CLKB,很显然当REGA或REGB前后有限漂移时OUT_CLK是不会出现毛刺的。

对GOOD电路有两个问题

1. SELECT如果在CLK下降沿左右发生变化该电路能否正常?

2. 该电路的触发器能采用上升沿触发吗?

请问,业界标准的做法是什么?

在《华为_大规模逻辑设计指导书.pdf》中提到,

通过组合逻辑对触发器的时钟在多个时钟中选择一个如下图所示:

上图中标为BAD的一个由于直接用组合逻辑实现在CLKA CLKB两个时钟中二选一的功能,而组合电路由于不同路径的延迟不同,所以在电路的时钟输出很容易产生毛刺。而标为GOOD 的一个由于对选择信号SELECT分别用两个触发器进行了同步化所以在时钟的输出端不会产生毛刺。

图1.29是图1.28中GOOD电路的原理时序图。其中REGA表示接CLKA的触发器,其对应的与门输出为REGA_CLK, 同样定义REGB和REGB_CLKB,很显然当REGA或REGB前后有限漂移时OUT_CLK是不会出现毛刺的。

对GOOD电路有两个问题

1. SELECT如果在CLK下降沿左右发生变化该电路能否正常?

2. 该电路的触发器能采用上升沿触发吗?

不错!

对GOOD电路有两个问题

1. SELECT如果在CLK下降沿左右发生变化该电路能否正常?

使用了R-S触发器的等价结构,所以正常工况下基本不会有毛刺

2. 该电路的触发器能采用上升沿触发吗?

用上升沿的话就可能在切换时钟时发生短暂的交越高电平脉冲,关键点在两个AND2上

不明白lz为何说要打两拍呢?亚稳态应该是对触发器而言的吧,对于组合电路毛刺而已。所以无需要用clock去打几拍。

好文,有礼了

高深呀!

我们ASIC里面是2级DFF

第一个问题,如果SELECT如果不满足CLK的hold 或者setup 时间是不是就有问题呢?

第二个问题是否可以详细说明呢,小弟不才,还不能理解清楚

select何时触发应该没有关系的吧

有意思。

可以,好东西

在公司的设计中只见过类似BAD这种。后面还是有不同,SEL与CLK之后又去毛刺电路。