用FPGA做的DDS有毛刺

时间:10-02

整理:3721RD

点击:

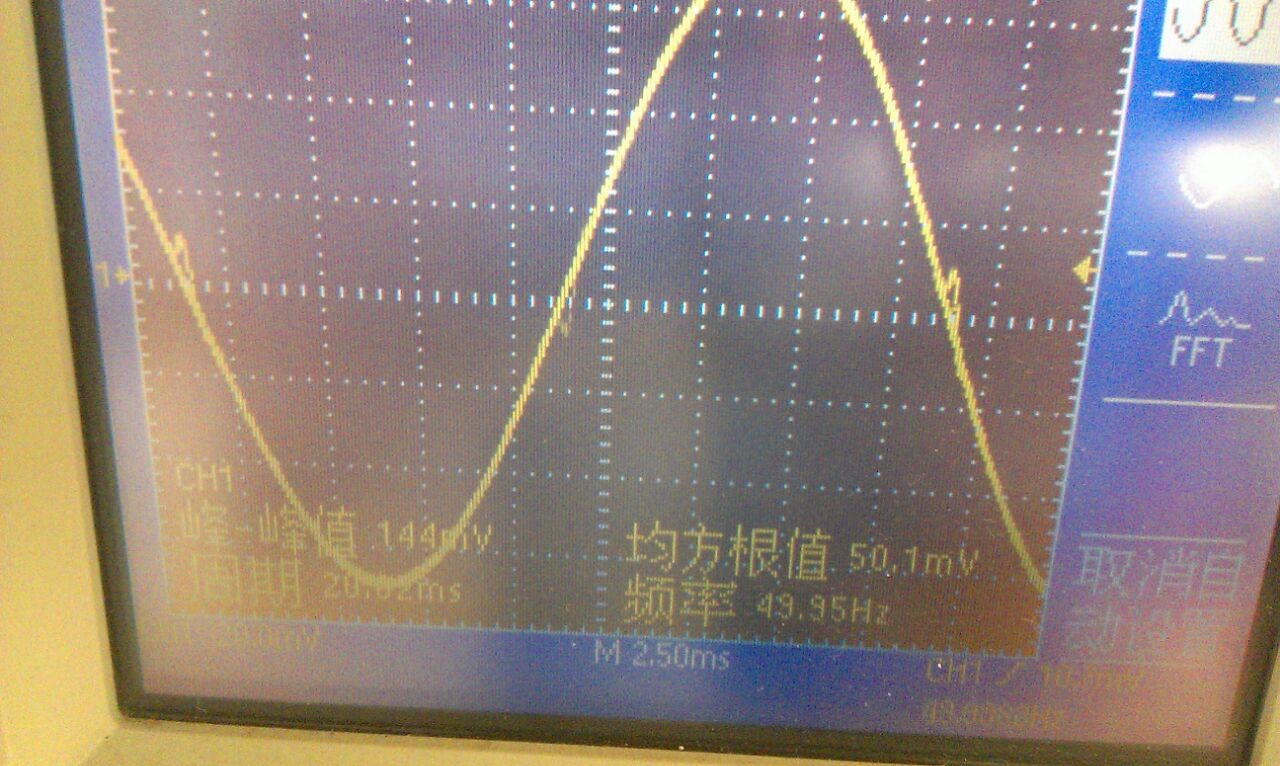

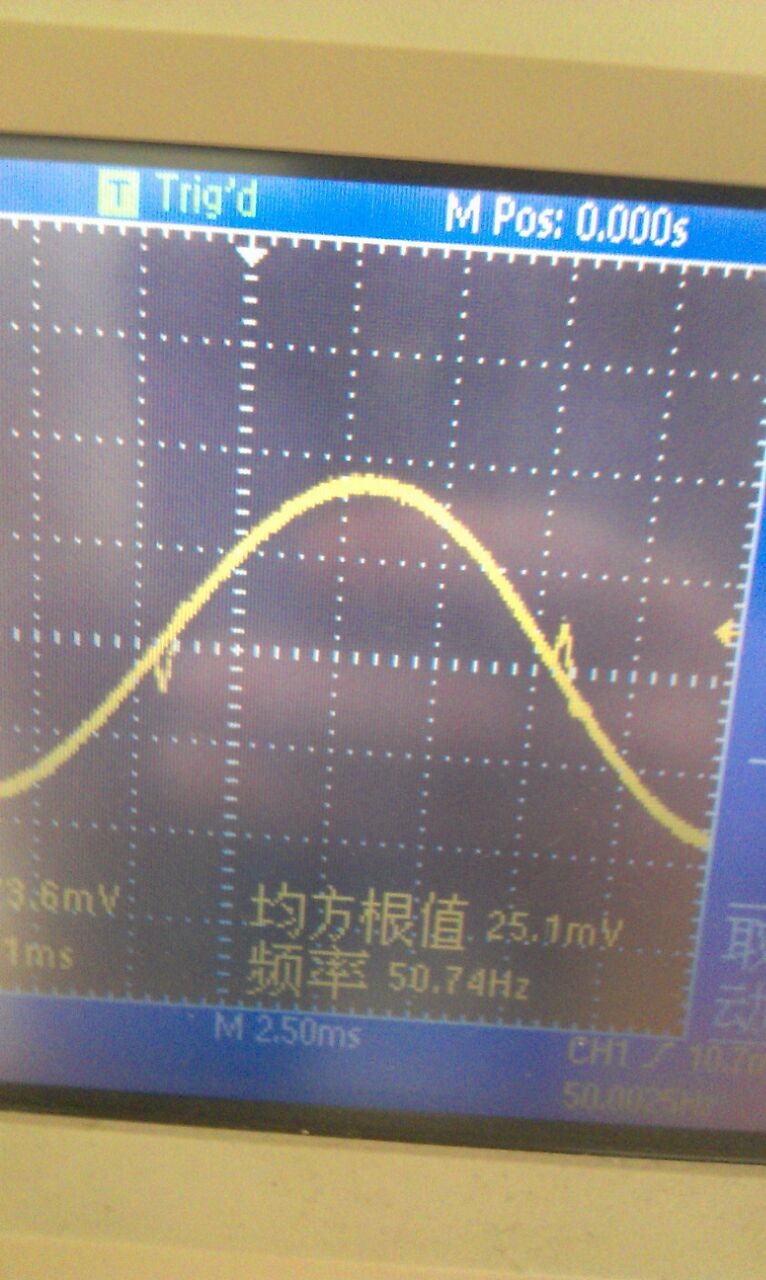

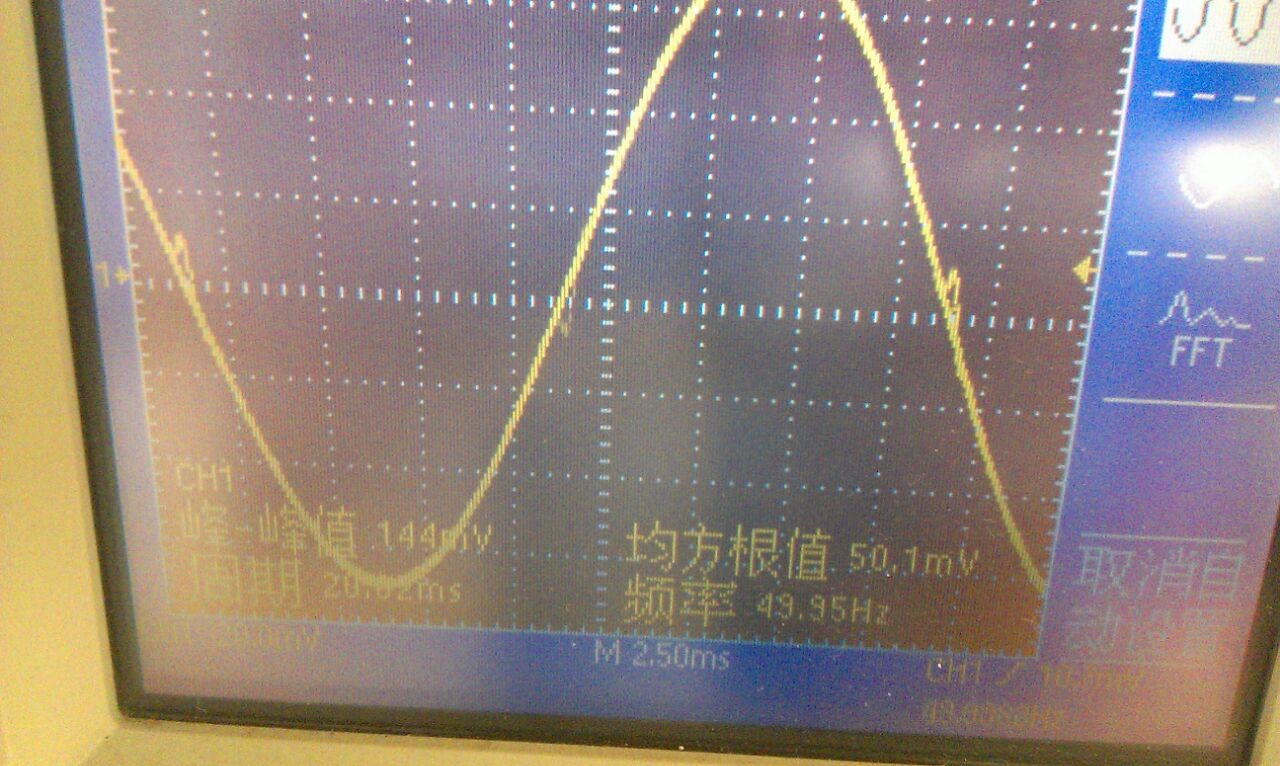

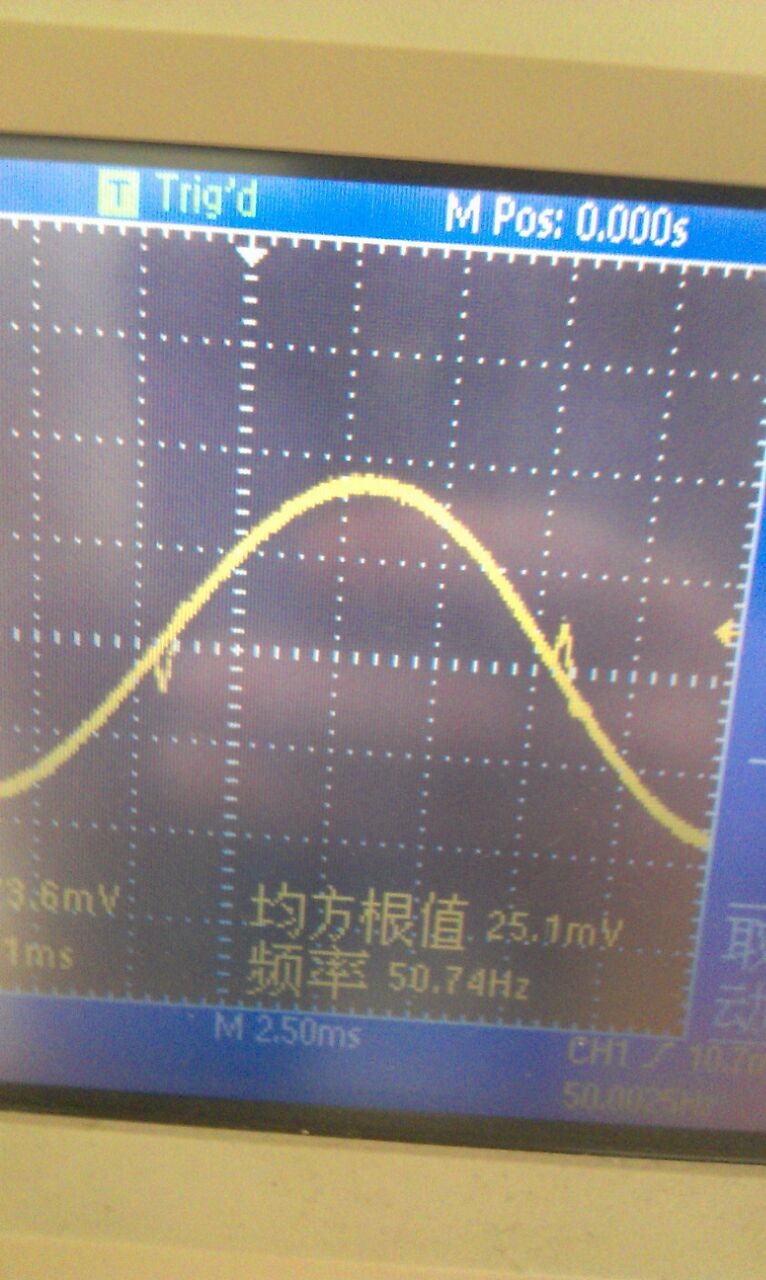

用DDS做的DDS正弦函数信号发生器,用示波器看有毛刺。综合后用modelsim仿真,输出波形并没有毛刺,很光滑。尝试了增加ROM点数,降低DDS时钟也没什么效果。ROM中存储了1/4周期点,DAC用的是串行的SPI口。

图片看到的是在0V附近有毛刺,如果降低正弦波函数,则毛刺就在其他地方。

图片看到的是在0V附近有毛刺,如果降低正弦波函数,则毛刺就在其他地方。

1 :输出的DDS数据与DA的时钟不匹配。2:1/4波形中的 地址选择位有问题,

建议后仿真看一下1/4

综合后DDS数据的每位触发器不是同时翻转,时钟偏移大,后仿能看到

用后仿真没看出有那个毛刺。弃掉1/4周期存储,改用全周期存储,也还是会有。不知是不是DAC时序问题,这个DAC没有时钟,其数据是串行SPI输入的,多通道的。这样好像很难保证时钟与数据同步。

小编你用的什么型号的示波器啊

高速DA数模转换模块(DAC900E),很适合用FPGA控制产生正弦波:

http://item.taobao.com/item.htm?id=25736860907

泰克的示波器

问题解决了。是DDS输出数据与DAC那边不匹配。用的是串行DAC,DAC没有时钟。谢谢各位好同志。

很好很好

这个不是毛刺,应该叫做掉码,一般情况为DDS输出与DAC部分的接口时序出了问题,很有可能是接口部分的时钟建立和保持时间不够,或时钟存在频差造成的

很好很好!

最好再加个高频滤波把毛刺滤掉。这样波形漂亮点。