xilinx fifo ip核 empty信号出错 求指导

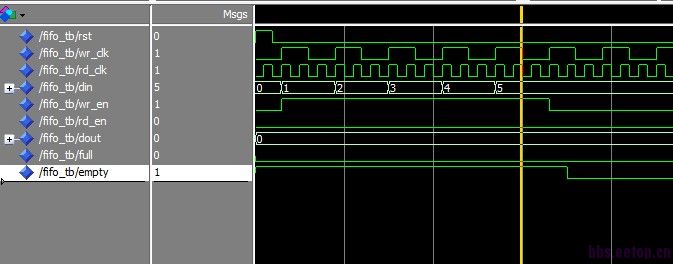

如图可见 数据已经送进去了,但是empty信号不在第一个数读入时变低,过了好几个数才变低,请问这是哪里出现问题了,谢谢大家

顶一下

哪位大神指导一下啊

FIFO深度是多少?empty设置的条件是什么样的?

gen ip的时候,是不是特别设置了empty的条件,看起来像是设置了那种将空的信号

感觉跟设置的fifo的低水线有关。

fifo 深度64 empty在哪设置啊 只有program empty可以设置吧 按理说读进去一个数 fifo中empty就应该变为0才对啊 怎么晚了这么久

full的信号设置了 empty没有特意设置啊

谢谢 能再说说低水线吗 可能fifo ip核就是这样的吧 看手册没看到时序图

FIFO IP有问题。

会不会输入位宽8,输出位宽32/40?就是输入输出位宽不一样

fifo 的 ip 没有问题。这个是empty 同步以后会出现delay,,如果你是mcu访问这个fifo 是否 empty 你需要加一组 empty 和 full 信号专门给mcu 看,,属于,同步和异步的问题

支持楼上的 要是Xilinx的IP的话 肯定不会有问题! 这个应该是经过一段Delay后, 才会显示

感谢 位宽是一样的 都是16位的

看来你只能再把这个ip生成一遍,看看有什么特别的地方。

查证一下wr_en是高有效还是低有效

请问小编问题解决了吗?我也遇到了一样的问题。纠结死了。

程序是不会骗人的

看手册 在看看你的复位信号

复位信号之后的4个周期左右FIFO的信号都是高电平

也就是这段时间不要操作fifo

看IP SPEC默认不设置的话,复位full,empty信号都会拉高一段时间,复位信号完成同步以后,empty信号才会接触

你自己去xilinx官网的Q&A上面找这样的问题,关键字是FIFO和EMPTY,然后你就明白了。Xilinx官网回答的很详细!

看看你的时钟线,是不是写的时钟和主时钟不一样,fifo的时钟慢,写的时钟速度快。

通过你的写使能信号,写的有问题,注意下,尽量写使能信号只保持一个时钟。

应该是异步FIFO的保护措施吧;这里的空和满都不是绝对的空和满;而是为了避免你产生错误的操作而提供的空和满信号;可以看看异步FIFO的论文,只要保证数据的安全,空满信号是有余量的;

从新产生个IP核测试下

这个有两个可能: 1 仿真时间单位和精度没有设置; 2 是verilog仿真时用了vhdl的仿真库

不知道小编的问题是怎么解决的?我最近也遇到了这个问题。我与发现FIFO的wr_clk和rd_clk有关系。

小编请问解决了吗?我也遇到这个问题了,写进去过一会儿才会拉低空信号

异步fifo就是这样,满和空都不会是准确的空满,都会多几个cycle,但是不会出现满空却没有把空满信号拉起来的情况