FPGA的触发问题,求解决

各位前辈,我有一个verilog代码,是实现在触发信号triggle_rising(检测triggle的上升沿)有效的时候,FPGA控制adc工作然后采集完1000个数据的时候,把数据存储在RAM中,然后通过RAM把数据传到另一块板子。但现在问题是下到板子上就“触发信号triggle_rising”FGPA检测不到,不知道问题出在那了,希望前辈帮我看看这个程序,看有什么地方需要改进的,指点一下,这是我写的代码,在FSM状态机的部分:

module fsm(

output [1:0] rw,

//output triggle_rising,

input spi_cs,

input full,

input triggle,

input clk

);

reg[1:0] state,next_state;

parameter S0 = 2'b00,

S1 = 2'b01,

S2 = 2'b10,

S3 = 2'b11;

reg sync_cs1;

reg sync_cs2;

reg sync_triggle1;

reg sync_triggle2;

reg triggle_low;

reg triggle_high;

wire triggle_rising;

//reg triggle_rising = 0;

reg [1:0] rwR;

assign triggle_rising = (triggle_low) && (!triggle_high);

assign rw = rwR;

always @(posedge clk)

begin

sync_cs1 <= spi_cs;

sync_cs2 <= sync_cs1;

sync_triggle1 <= triggle;

sync_triggle2 <= sync_triggle1;

triggle_low <= sync_triggle2;

triggle_high <= triggle_low;

// triggle_rising <= (triggle_low) && (!triggle_high);

end

always @(posedge clk)

begin

state <= next_state;

end

always @(state,full,sync_cs2,triggle_rising)

begin

rwR = 2'b00;

next_state = S0;

case(state)

S0 : begin

if(triggle_rising)

next_state = S1;

end

S1 : begin

rwR = 2'b01;

if(full)

next_state = S2;

else

next_state = S1;

end

S2 : begin

next_state = S2;

if(sync_cs2)

next_state = S3;

end

S3 : begin

rwR = 2'b10;

if(full)

next_state = S0;

else

next_state = S3;

end

endcase

end

endmodule

不是发过一次了me?

1. 你确定triggle和clk是在一个时钟域的吗?是否太短导致sample不到。 2. 做个仿真吧,你会看到一堆unknown信号,可以试着把你这些做double flop的信号,给个复位撒,控制逻辑信号最好做到能复位。

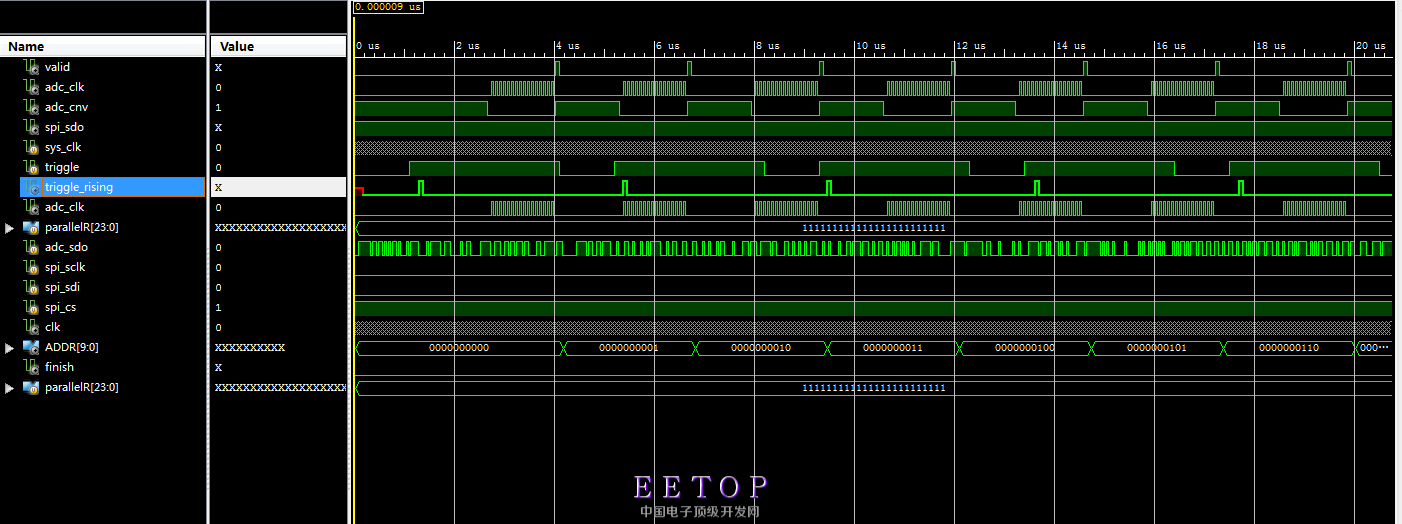

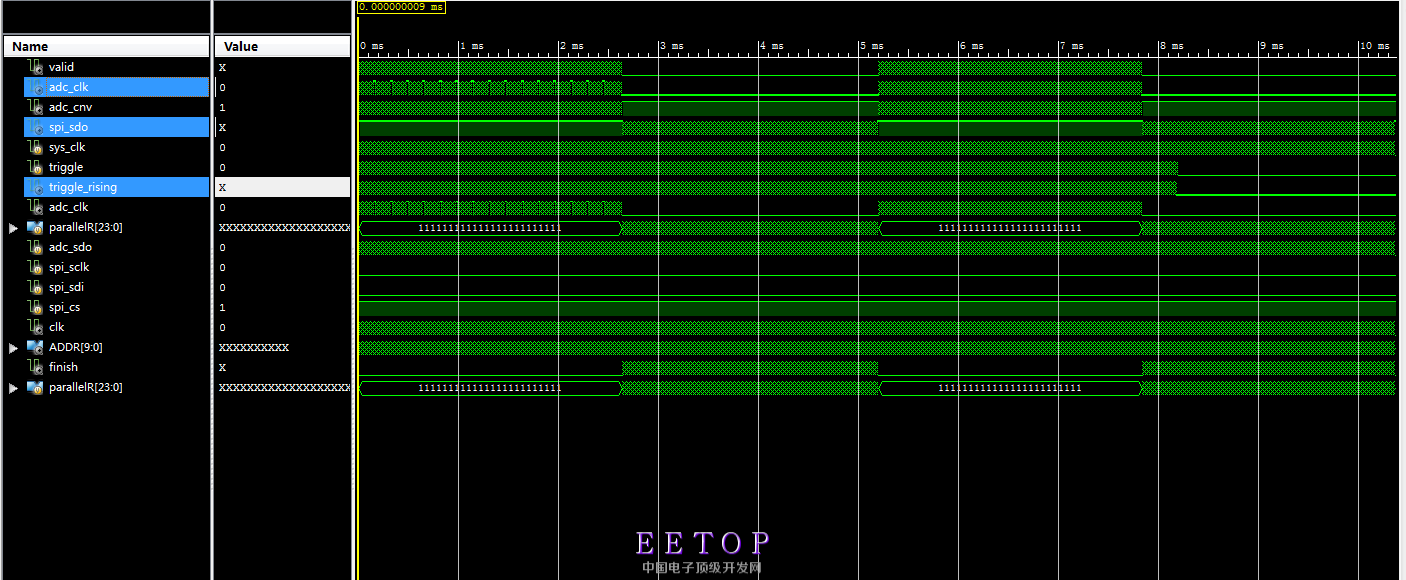

是这样的,我之前也想到是不是同步的问题,于是我把检测triggle上升沿的triggle_rising信号放在always块中,但试过了还是不行,仿真这些都是正确的[img]file:///C:\Users\Administrator\AppData\Roaming\Tencent\Users\736862923\QQ\WinTemp\RichOle\NU7U~C7QJXQ}U_AOY@DZT_P.png[/img]

前辈说的double flop 是什么意思啊

前辈说的太短,我也考虑过这个问题,是一个时钟,但我单独把triggle_rising引出来,是可以检测到这个信号的,并且刚好是一个时钟周期,所以这个加宽这个信号,该怎么做呢?求解答

打两拍,或上

打两拍,是把triggle_rising加宽2个时钟周期吗

你需要明确设计中的triggle和clk是不是一个时钟域的,如果不是的话,你输入打拍很可能是没用的,至少是不稳定的。