正弦信号源如何调节峰峰值?(FPGA+PWM+DDS实现)

时间:10-02

整理:3721RD

点击:

最近想了好一阵子这个课程设计,谢谢各位帮助,解决了频率调节问题,但是我不是很理解如何调节输出信号峰峰值0.1V~2V

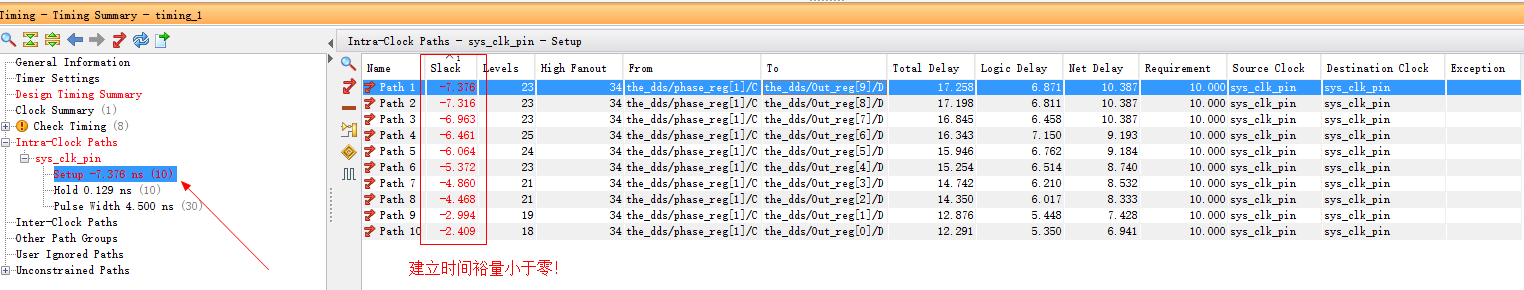

有人说“在正弦值乘上幅度系数来缩放”,但是我直接修改dds的out,结果综合分析出现时序不满足的问题

就是这样: Out <= (sinTable[addr[PHASE_W - 1 : PHASE_W - TABLE_AW]])/20*Amplitude;//Amplitude是我在top用按键可调的reg

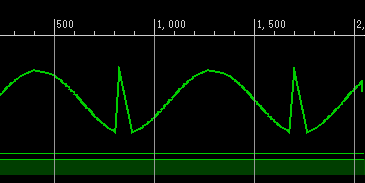

最后下载到xilinx板子上,用ILA调试的结果很奇怪,之前没加上调幅的amplitude还是正弦波。

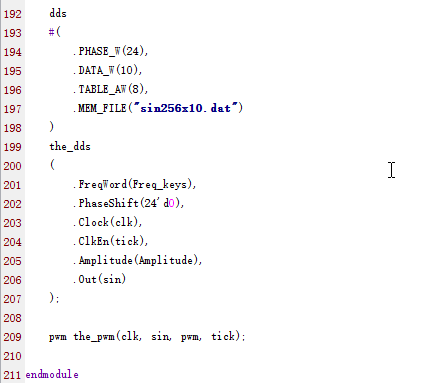

最后贴上问题源代码吧!

- module dds

- #(

- parameter PHASE_W = 24,

- parameter DATA_W = 12,

- parameter TABLE_AW = 12,

- parameter MEM_FILE = "SineTable.dat"

- )

- (

- input [PHASE_W - 1 : 0] FreqWord,

- input [PHASE_W - 1 : 0] PhaseShift,

- input Clock,

- input ClkEn,

- input [5:0]Amplitude, //amplitude control

- output reg signed [DATA_W - 1 : 0] Out

- );

- reg signed [DATA_W - 1 : 0] sinTable[2 ** TABLE_AW - 1 : 0]; // Sine table ROM

- reg [PHASE_W - 1 : 0] phase; // Phase Accumulater

- wire [PHASE_W - 1 : 0] addr = phase + PhaseShift; // Phase Shift

-

- initial

- begin

- phase = 0; Out = 0;

- $readmemh(MEM_FILE, sinTable); // Initialize the ROM

- end

-

- always@(posedge Clock)

- begin

- if(ClkEn)

- phase <= phase + FreqWord;

- end

-

- always@(posedge Clock)

- begin

- if(ClkEn)

- Out <= (sinTable[addr[PHASE_W - 1 : PHASE_W - TABLE_AW]])/20*Amplitude; // Look up the table

- end

-

- endmodule

相关源代码:

完全不理解,为什么直接在verilog对out乘除就会让它时序不满足

你的查找表内容少了一个点吧,比如四分之一周期是512个点,你应该按照513个点来实现。细节你多考虑下

时序不满足是因为时钟要跑100M,不能简单用除法,而是应该用位移运算符

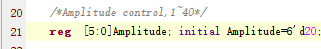

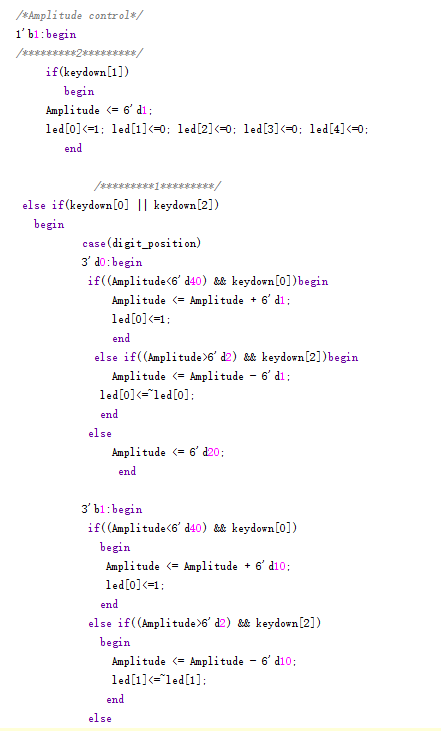

我的问题其实应该是这样的:我的信号发生器不用硬件的增益反馈,而是通过乘法器将输出幅度控制!但是现在是左位移会丢失高位,只能右位移,意味着只有小于或等于1Vpp的值