关于时序分析,时钟输出延时

时间:10-02

整理:3721RD

点击:

- module exercise (

- clk,

- reset,

- in_1,

- in_2,

- out_1,

- out_2);

- input in_1,in_2,clk,reset;

- output [3:0] out_1,out_2;

- //nei

- reg [3:0] a,b,c;

-

- assign out_1=c;

- assign out_2=a;

- always @(posedge clk or negedge reset)

- begin

- if(!reset)

- begin

- a=0;

- b=0;

- c=0;

- end

- else

- begin

- if(a>8)

- a<=0;

- else

- a<=a+1;

- case ({in_1,in_2})

- 2'b00: c<=a+b-1;

- 2'b01: c<=8-a+b;

- 2'b10: c<=a+b+1;

- default:c<=0;

- endcase

- b<=c;

- end

- end

- endmodule

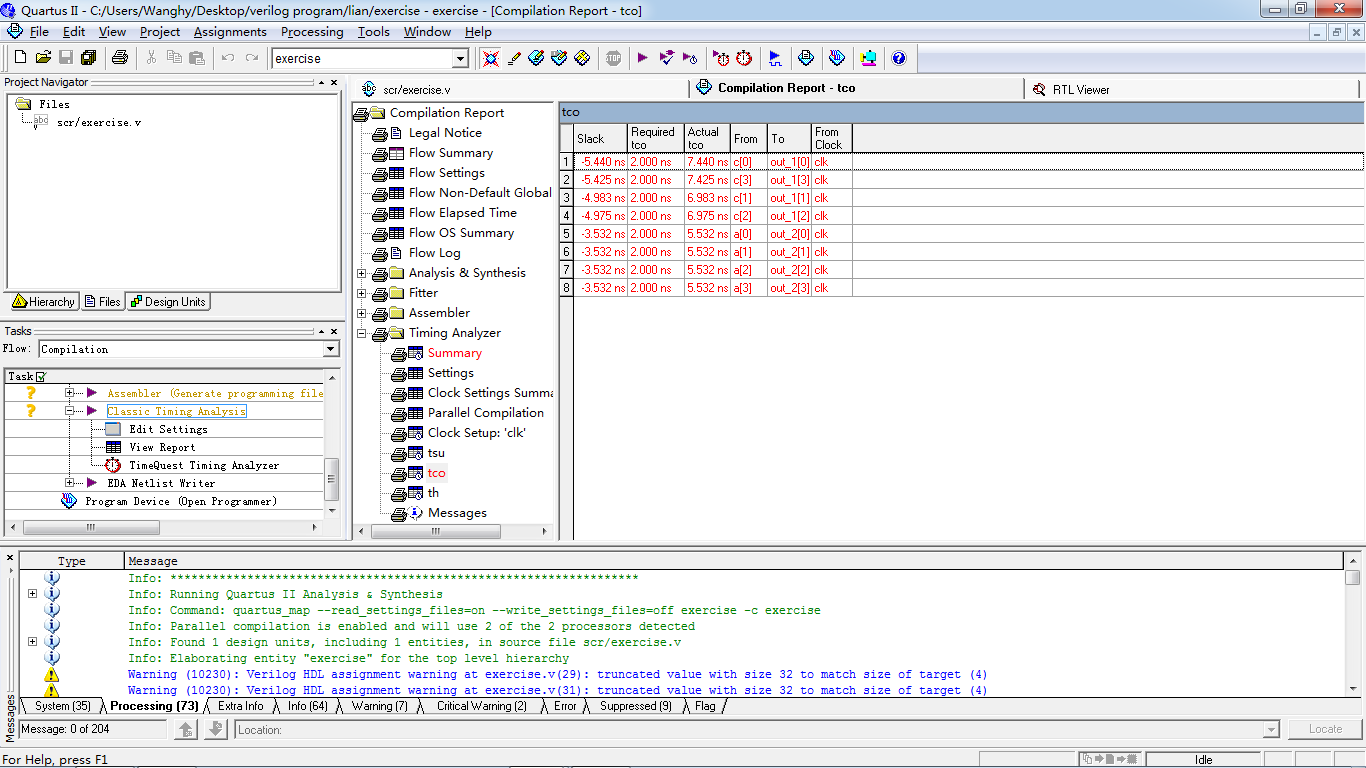

这是我为了学习时序分析随便写的程序,其中对于a来说,只是简单的自加,到9后归0。而时序分析后从a到out_2的时钟输出延时(tco)为什么这么大?这是正常的吗?如果想弄小一点应该怎么办?

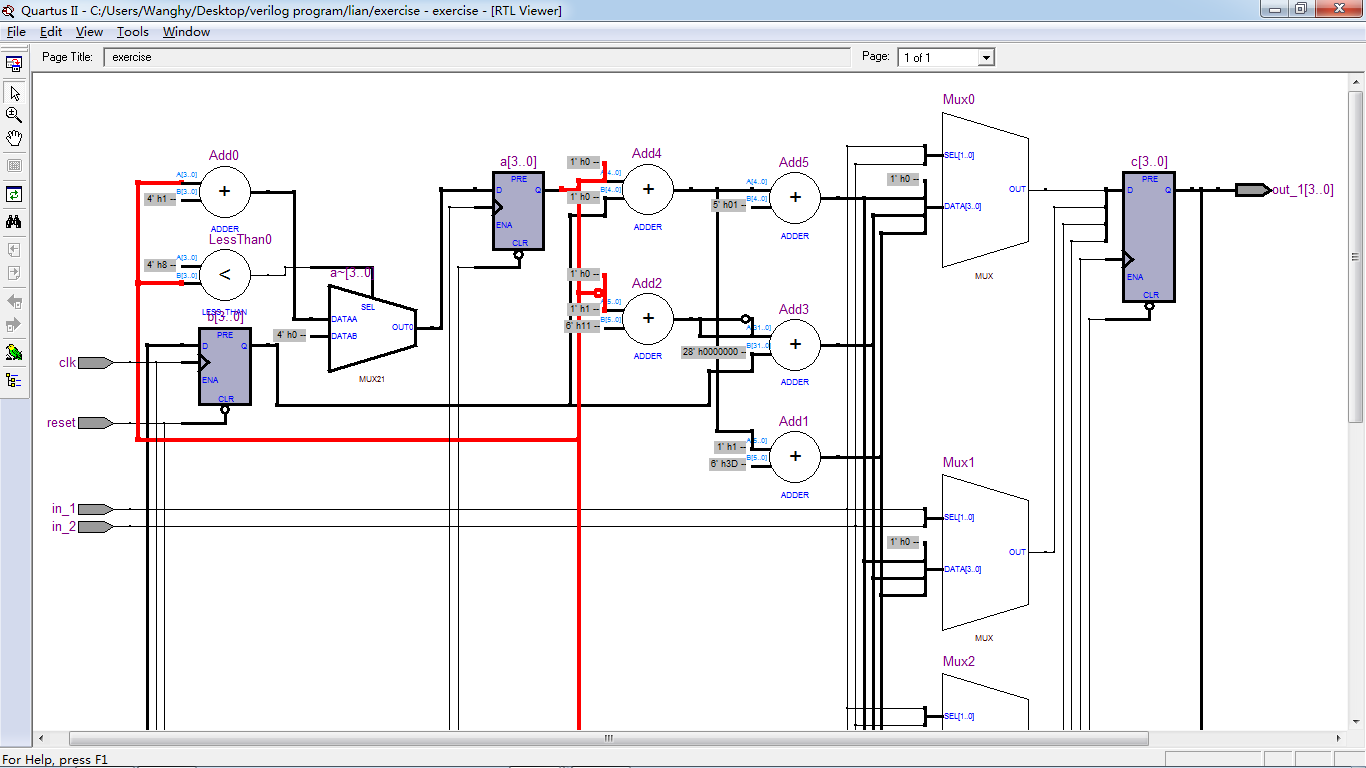

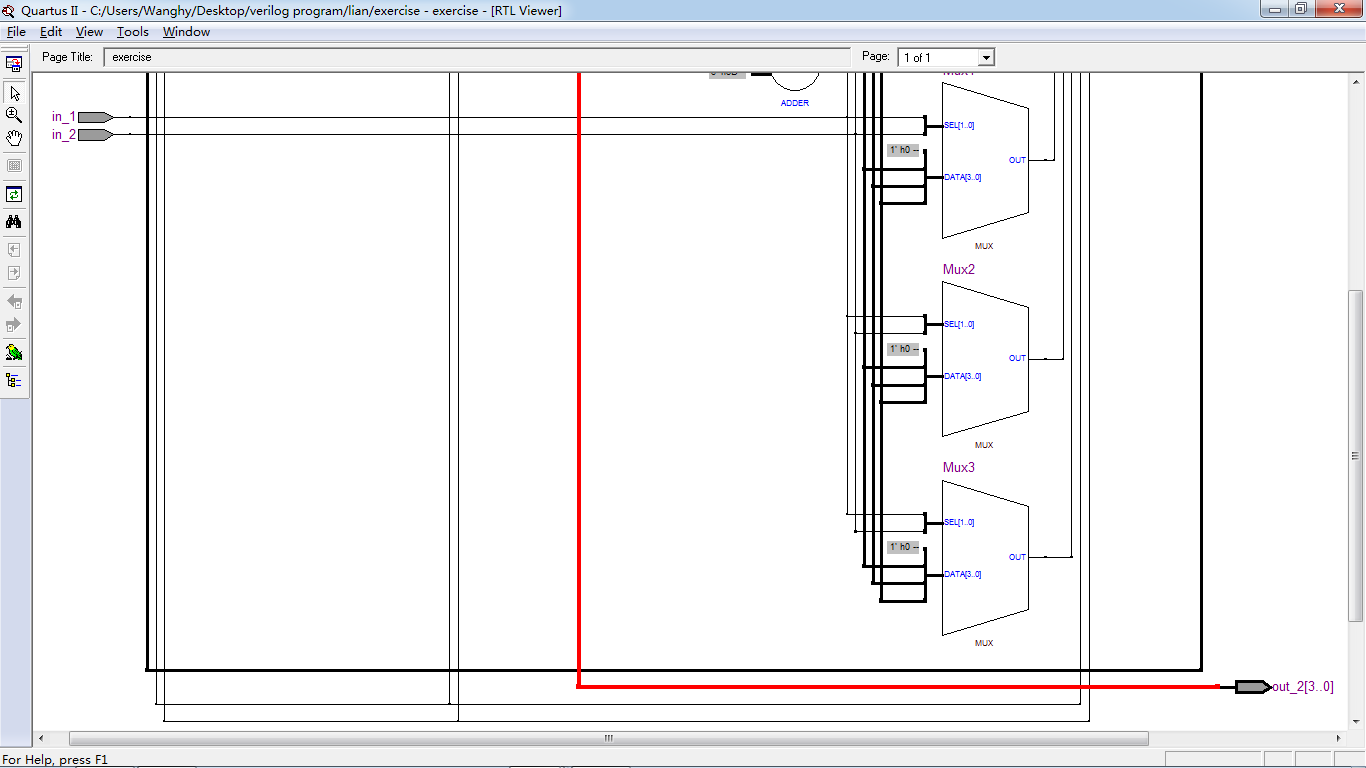

这是RTL图:

这是RTL图:

谢谢!

谢谢!

这个OUT2是直接到PIN脚上去的吧,这个没办法,因为PIN脚输出要驱动一个很大的电流,延迟一般都比较大,你可以试试把a赋给OUT2的时候用时钟打一拍,把IOB上的REG用上,会好一些。

谢谢你,原因我知道了。不过如果是驱动大电流的原因那为什么要打一拍?还有“把IOB上的REG用上”是什么意思?能具体点吗?谢谢!

PIN脚附近还有一个REG,用上可以减少输出延迟

知道了,谢谢!