求解答:关于示波器测试时模块激励产生问题

时间:10-02

整理:3721RD

点击:

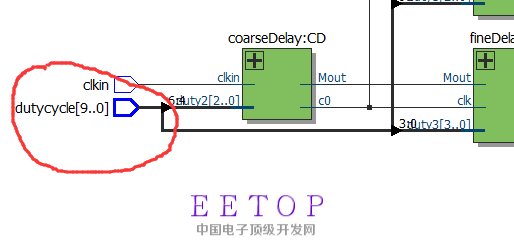

模块的输入是这样的,有一个输入为10bits的数据流

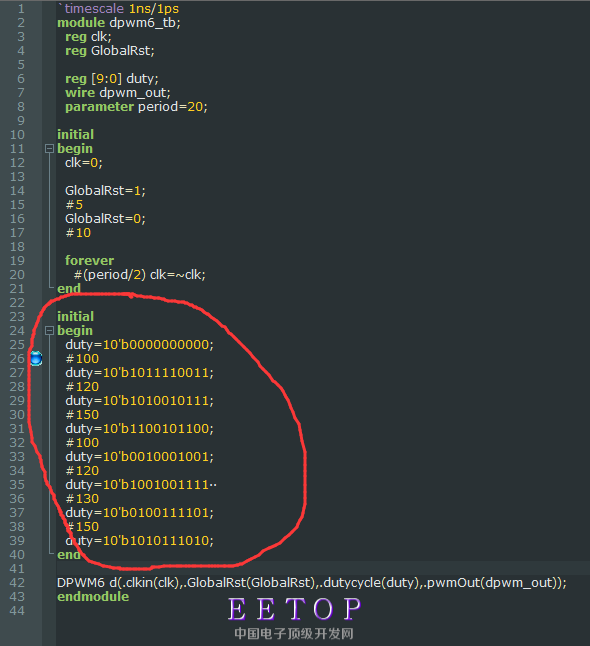

如何用示波器测试时,让10bits数据流产生以下变化,是不是用状态机。?

求解答。谢谢

1.你写的#只能用来仿真,是想用fpga生成TB对应的波形么?

2.如果你的想法是(1),要产生序列用状态机或者用rom都可以,但实现相应的#100,#150可能需要比较高频的时钟,你需要确认你的fpga是否支持。

3.示波器我还没见过有10个通道的,你可能需要逻辑分析仪来观察结果。

1.你的TB文件只能用来仿真,产生不了波形;

2.可以直接计数来确定数据输出的时间

前面正解,不用状态机都可以,就是用条件语句判断就行了。

你可以用一個clock去計算,當計算到你想要的時間的時候,就輸出你想要的值.

這樣會比寫FSM簡單.