综合时时钟约束设置问题

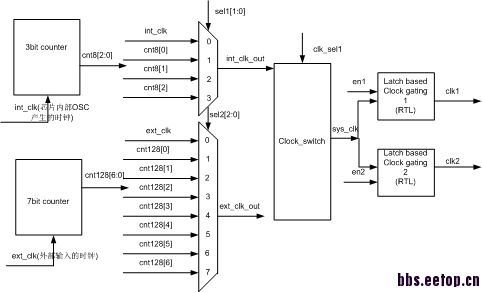

目前的芯片具有如下的时钟结构,DC综合时碰到一些问题,主要是由于有多时钟源,然后不同的时钟分频,再经过时钟切换和门控时钟产生真正使用的时钟,不知道如何完整正确的对创建时钟并进行约束,包括create master 时钟generated时钟,请教达人指点!

补充说明

在脚本中,将int_clk和ext_clk都定义为master clock,其中ext_clk加了 add选项,然后想把他们给分频后的时钟作为对应的generated clock,

如下

create_generated_clock -name int_clk -source u_ic/u_clkgen/int_clk -divide_by 1 [get_nets u_ic/u_clkgen/int_clk_out]

create_generated_clock -name ext_clk -source u_ic/u_clkgen/ext_clk -divide_by 1 [get_nets u_ic/u_clkgen/ext_clk_out]

报错提示如下

Ignoring all 1 objects in collection '_sel18' because they are not of type port, or pin. (UID-445)

Error: Value for list 'source_objects' must have 1 elements. (CMD-036)

感觉是因为工具找不到source_objects,这里应该是int_clk_out和ext_clk_out,从上图可知,这两个都是mux的输出,不是模块的port也不是cell的pin,所以我选择了get_nets,这是否有问题?

几个问题

1 int_clk和ext_clk是不是必须定义为主时钟点,即master clock?

2 上述主时钟后有三级处理,分别为分频后的时钟int_clk_out和ext_clk_out(第一级),时钟切换clock swith后的时钟输出sys_clk(第二级),以及门控时钟后的时钟clk1和clk2(第三级),这几级的时钟是否都应该设置为generated clock?还是可以跳过其中的某一级?3 因为采用的标准单元中没有门控时钟单元ICG,因此时钟门控这里是自己用代码写的,基于latch的门控,在综合的时候需要做什么设置,是否还要加诸如set_clock_gating_style -sequential cell latch .......以及相关的约束?

4 能否给个参考的脚本?

顶一下

首先是你的两个int_clk and ext_clk 不是顶层的PORT那就是内部的pin, 你如果想在(当然也可以)在这里创建时钟, 你就用给 create_clock [get_pins u_ic/u_clkgen/int_clk] -name int_clk , ex_clk也一样, 然后你在分频后的地方创建分频时钟, 至于你的mux 时钟 你就用set_case_analysis 将MUX的选择信号置0或者1, 让通路选择最紧的时钟 就可以了 最后 门控时钟的地方需要加约束

谢谢,我是想把分频后的时钟int_clk_out和ext_clk_out定义为generated clock但是不管用get_pins还是get_nets工具都提示找不到这个对象,即create_generated_clock -name int_clk_out -source u_ic/u_clkgen/int_clk -divide_by 1 [get_pins u_ic/u_clkgen/int_clk_out] 或者

create_generated_clock -name int_clk_out -source u_ic/u_clkgen/int_clk -divide_by 1 [get_nets u_ic/u_clkgen/int_clk_out] 都出错,不知道是不是因为int_clk_out和ext_clk_out不是u_clkgen模块的输出时钟,而只是u_clkgen模块内部的信号的关系? 如果要将int_clk_out和ext_clk_out改成输出port应该可以,但是我不想这么做,因为芯片内部真正使用的时钟是后面经过门控后的时钟,也就是上面的clk1和clk2,他们是u_clkgen模块的输出端口。 请问我如果不改RTL,这些约束该如何设置?

请问这个问题解决的了吗,我也遇到了类似的问题

请教,有后续进展吗?

看需求而定。

如果最后的clk1与clk2需要同步,需要定义create int_clk, create ext_clk, create sys_clk即可;

如果最后的clk1与clk2不用同步,需要定义create int_clk, create ext_clk, create clk1, create clk2即可。

建議只要對clk1,clk2下Timing constraint即可.

即是create clock在clk1和clk2.

因為clk1,clk2之前的電路應該算是clock generator的電路,

是比較沒有辦法下Timing constraint,加上又是非同步.