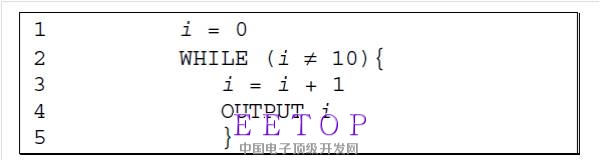

如何根据伪代码画出正确的datapath和状态图?

时间:10-02

整理:3721RD

点击:

有时候会发现画出的状态图和datapath里时序有错误,与伪代码不对应

是否有合理的顺序去解决这种问题呢?

自己写verilog代码综合一下就可以了

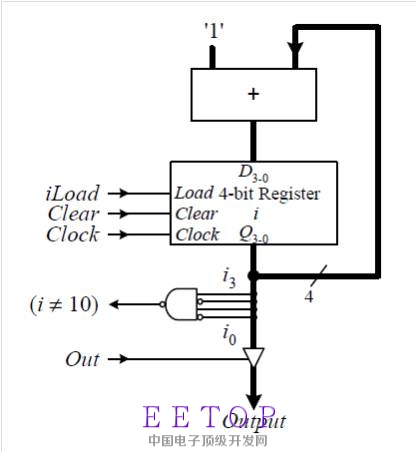

我根据你的意思,写了个code,仅供参考。另外,其实我对datapath里面"OUT->"不是很理解什么意思。

- module data_path(

- input wire clk,

- input wire clear,

- output reg [3:0]i,

- output reg [1:0]state);

- parameter state0 = 0;

- parameter state1 = 1;

- parameter state2 = 2;

- parameter state3 = 3;

- reg [1:0] next_state;

-

- always @ (posedge clk or posedge clear)

- begin

- if (clear)

- state <= state0;

- else

- state <= next_state;

- end

- always @ (posedge clk or posedge clear)

- begin

- if (clear)

- i <= 0;

- else

- i <= (i != 10) ? i + 1 : i;

- end

-

- always @ (state or i)

- begin

- case (state)

- state0: begin next_state = (i != 10) ? state1 : state3; end

- state1: begin next_state = (i != 10) ? state2 : state3; end

- state2: begin next_state = (i != 10) ? state1 : state3; end

- state3: begin next_state = state3; end

- endcase

- end

-

- endmodule

自己写verilog代码综合一下就可以了