一个verilog关于时钟的面试题

最近碰到一个面试题,不知道怎么解决,望高手指点

用Verilog/VHDL实现一个clock generator 。要求如下:

a、实现2分频和4分频

b、使两个输出时钟的skew尽可能小

c、受外部噪声影响后,该电路功能可以自行恢复

两个时钟是要输出到FPGA管脚吗?如果是的话,可以用DDIO打出去,这样两个时钟的skew基本是一样的。

对于skew,我认为是这样子的。

对于二分频,从clk到clk2f ,delay是:1个 tco 以及1个 td(反相器 )的延时

对于四分频,就是两个tco,两个td。

那么我在二分频输出之前,增加一个反相器以及一个寄存器就会比较好了。

同意楼上

这个题目的要求是用VERILOG实现,我认为说的意思应该是不依赖宏单元实现。至少考到的知识点是两个产生的时钟应该打两个拍子后输出,至于说自恢复,不是很明白。

二分频的话,应该是一个DFF的Q接一个inverter到它的D,那么delay应该是Tc2q吧,为什么要把inverter的delay算进来呢?不过你的思路应该是对的

你说的打两个拍子是指?

另外,那个自动恢复你有什么想法呢?我在想是不是可以通过某个电路实现反馈,把reset变成1,这样就可以恢复了,但是没有具体的办法。

在低频的时候,反相器延时一点点不重要,比如说500ps,对于几十兆的时候对相位的影响不大。

但是,在高频的时候,比如说500MHz的时候,周期才2ns,对于500ps就是90度相位了。

我想,要求对于skew那么严格,应该就是频率很高了。

所以,把反相器的延时算进去。

对于自行恢复,我没搞明白怎么自行恢复。

always @( posedge clk

clk_divide_by2 <= ~clk_divide_by2

二分频

但是自恢复不知道

两时钟skew尽量小,就用高频时钟都打一拍就行了,没那么麻烦

感觉没有3楼说的那么复杂,一般面试侧重基础知识的功底

因为既然是内部分频,一般频率不会过高;

高了就直接DCM/PLL了,如果用verilog实现很高的时钟分频,这个考题完全没有实用价值

考官应该主要在于考察门控时钟及同步设计的思想

供参考

分频的方法倒是很多,就是不明白受到外部干扰之后怎么进行时钟恢复?

我觉得自恢复说的是不是,状态机的编码的时候,无效状态都能自动跳回到有效状态。这个来考虑设计的counter?

reg [1:0] cnt;

always @ ( posedge clk )

begin

cnt <= cnt + 1'b1;

end

wire clkdiv2 = cnt[0];

wire clkdiv4 = cnt[1];

clkdiv2和clkdiv4的时钟都是clk->q,所以skew是一样的。 cnt被干扰后最后都会是00->01->10->11。所以会恢复。

对于RTL设计而言, skew尽量小有些误导了。

只要是同步设计, 在满足step的前提下, skew是来自于时钟网络本身的skew。

这个skew是电路实现的问题, 而不是设计能解决的。

只要你不是用ripple这样的结构分频, 别管是计数器还是状态机,实现的结果是一样的。

skew要在设计实现的时候去约束,对于FPGA, 直接用PLL是最有效的。

对于ASIC, skew是在做CTS的时候考虑的。

对于干扰的问题, 说要自恢复, 显然是说不能因为干扰死机之类的, 对于ripple或则计数器

这样的方法, 不存在死机的问题。 对于状态机,可能要考虑默认状态的问题。

然而无论什么方法, 如果干扰来自时钟本身, 即使自恢复了, 时钟本身还是会产生glitch

这个glitch会导致逻辑出错, 原本的同步设计也不同步了, 系统也会混乱, 恢复了也没有用。

呵呵, 不过恢复了, 总比啥也不做好吧。

这位大大可能想复杂了。实际上skew尽量小的意思就是同时钟域,这样一般都是尽量小的。 恢复的话,既然人家说了只要能恢复并且也不规定时间那么也不用考虑那么复杂,能恢复就行了,能恢复的东西最好就是类似moore机这样的与输入无关的东西,最简单的就是无使能的计数器拉。

觉得这种解释比较靠谱。

可以设置受到噪声影响的标志位,例如,将受到噪声影响的结果表现为clk_2div或者clk_4div持续高电平或者持续低电平,可设置一个寄存器来对持续高电平或者低电平的时间进行计数,当计数值超过一定限度时,把reset拉高(假设高电平复位),过几个时钟周期后再拉低reset,这样一来就实现了自恢复。

对于skew,我认为是这样子的。

对于二分频,从clk到clk2f ,delay是:1个 tco 以及1个 td(反相器 )的延时

对于四分频,就是两个tco,两个td。

那么我在二分频输出之前,增加一个反相器以及一个寄存器就会比较好了

小编说的很好···我顶他···

对与回复可不可以用状态机实现啊

用两次D触发器,消除毛刺

3楼说的是对的,不考虑wire delay的话,两者之间相差一个tco+td。

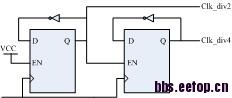

[attach]385607[/attach]

好想这个skew很小,也能自恢复吧。其实也是楼上用verilog写的模四计数器也差不多,菜鸟望指点!

说得对

貌似这种回答比较好

看看。

小编说的对 以原始的clock信号参考,4分品的比2分品的多了一个clock2q delay

不怎么理解

想法很好,应该是这样解释