用verilog写可综合的循环语句

时间:10-02

整理:3721RD

点击:

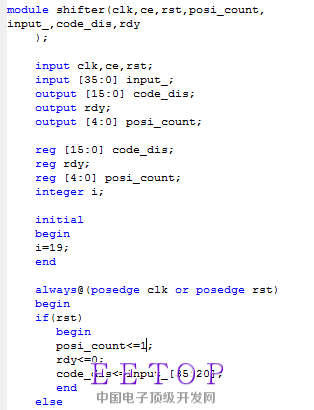

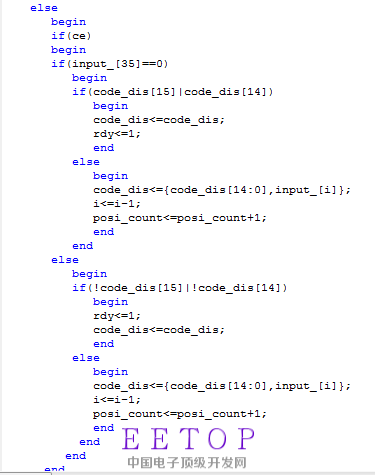

我打算用verilog写一个16位的移位寄存器,要用到循环,目标是提取36位的一个数的有效位数,如果最高位是0,则把高位是0的位数舍去,取16位。就必须要给计移位的integer赋初值,我现在用的是initial模块赋初值,但是这个在综合时候是会被忽略掉的,有什么其他赋初值又可综合的办法。没有用for循环,因为for循环到综合的时候又特别占资源,我就是为了节约资源才取有效位的。请各位大神帮忙

啊,图片发出来位置乱了,还是自己顶一个

又是我自己在说,暂时是在这个时序电路里用一个同步复位信号赋初值

initial不能综合,可以在复位的时候赋处置,引入reset复位

可以尝试在复位中赋初值

同步复位信号? 这复位信号rst跟时钟没关系呀,应是异步信号吧?

因为这是一个非常小的模块,后来就将全局的异步复位信号reset改成了这个小模块的局部的同步复位信号sclr