菜鸟请问:关于时钟sdc约束的问题

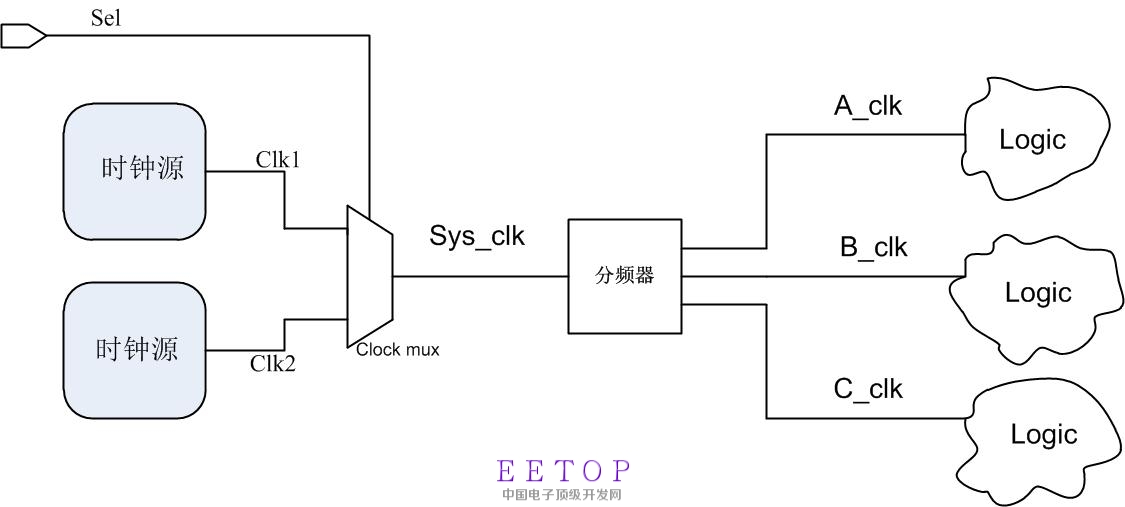

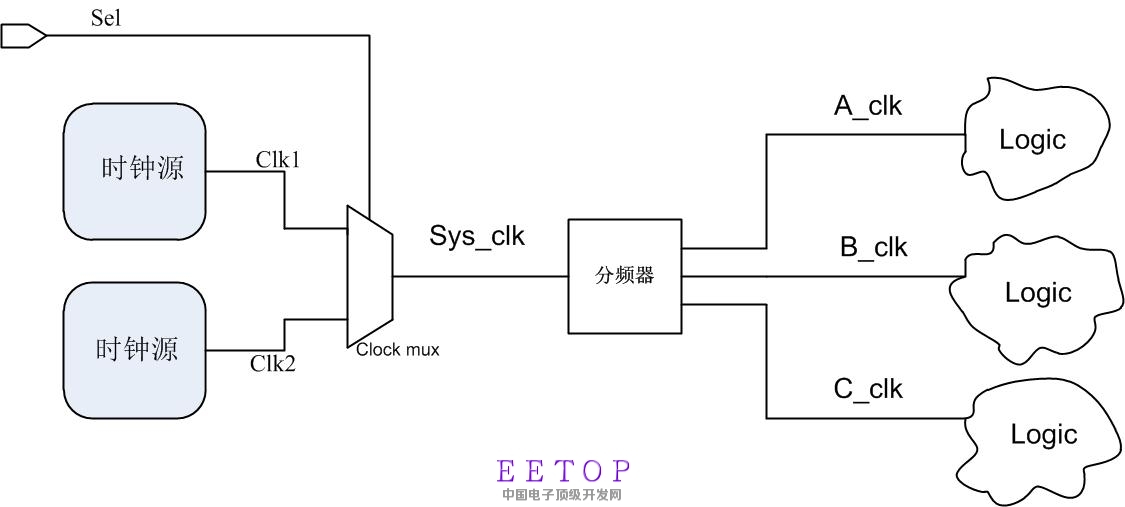

请问例如上图的系统时钟,我应该用什么sdc命令约束时钟,

create_clock 在时钟源(晶振)的输出引脚上吗?

clock mux怎么约束?set_case_analysis吗(关于这些有点模糊)

还有分频器怎么约束?

多谢各位前辈指教!

没看明白你说的是什么

就是比如图中的时钟模块,我们一般怎么约束啊

时钟源create clock,分频器输出create generated clock,clock mux可以不用约束,这样clk1,clk2都能穿过mux;

还是附带小编的图来进行说明:

首先,将两个时钟源 分别使用create_clock 的方式进行周期约束,然后就是进行sys_clk的 约束,一般来讲可以是set_Case_analysis 0 [get_pins sel] 这样的话,就告诉综合布局布线工具,同一时刻只允许一个时钟源通过,否则工具默认的是同一时刻,这两个时钟都和sys_clk有关系,这个约束更有点特殊例外约束的意思,经过实践验证也可以正常工作,不过一般建议使用:

set_clock_groups -physically_exclusive方式,进行物理独立,因此小编的约束又可以这样:

create_clock -name clk_mode0 -period 5 [get_ports clk1]

create_clock -name clk_mode1 -period 4 -add [get ports clk2]

set_clock_groups -physically_exclusive \

-group [get_clocks -include_generated_clock clk_mode0] \

-group [get_clocks -include_generated_clock clk_mode1]

当然上面的时钟周期是我随便定义的,可根据实际情况修改

太感谢了

物理独立表示两个时钟不会同时存在,最好用于一个引脚上可能输入几种不同的时钟频率。

逻辑独立表示两个时钟可以同时存在,但最终只有一个时钟有效,一般用于MUX的输出时钟。

如果不进行Delta delay等分析,两种貌似都可以,但是如果考虑了delta delay,LZ上面的最好是用逻辑独立。

嗯,感觉七楼分析的有理

恩呢,分析的很透彻

那那个分频器产生后的三个时钟间也要设置成clock group吧还是设置成false path?

分频器后面那三个时钟也要设置clock group吧,还是false path?

这个 问题是这样的,首先你是如何分频的? 通过RTL逻辑吗? 如果是的话,那么那三个时钟最好使用create_clock的方式约束时钟,如果是fpga内部的时钟管理单元的话,就不需要,另外这个三个时钟是在一个时钟产生的,所以是同源时钟,一般来讲不能使用false path, 但是某些特殊应用也可以设置false path。 这个问题能不能设置成false path 是要根据你的逻辑设计来分析的,不能一概而论。

首先可以直接create_clock -name sys_clk $location_sys_clk -period xxx , 至于clk1和clk2是否要create_clock,在你这个例子中并不重要,当然定义为create_clock也不会有问题。

后面分频器出来的三个时钟,如果需要跟sys_clk同步,则使用

create_generated_clock -name a_clk $location_a_clk -source $location_sys_clk -divide_by X

create_generated_clock -name b_clk $location_b_clk -source $location_sys_clk -divide_by Y

create_generated_clock -name c_clk $location_c_clk -source $location_sys_clk -divide_by Z

如果不需要跟sys_clk同步,则使用

create_clock -name a_clk $location_a_clk -period xxx

create_clock -name b_clk $location_b_clk -period yyy

create_clock -name c_clk $location_c_clk -period zzz

如果a/b/c三个时钟跟sys_clk同步,set_clock_groups -asynchronous \

-group {sys_clk a_clk b_clk c_clk}

如果都是异步的,

set_clock_groups -asynchronous \

-group {sys_clk} \

-group {a_clk} \

-group {b_clk} \

-group {c_clk}