求助,SPI从机verilog编码

本人初学verilog,认识尚浅,求各位大神指导。

最好能有代码参考参考

从机可以自己写个协议,规定第几次数据表示地址

如果主从设备都是你自己设计的 你就可以自己约定数据的组合方式 比如 读写+地址+数据 或者 地址+读写+数据等, 如果你的从设备适应人家的主设备 你就要去查看主设备的约定。

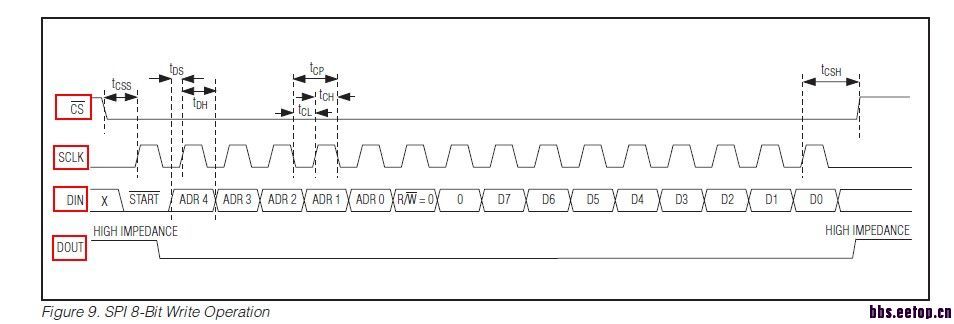

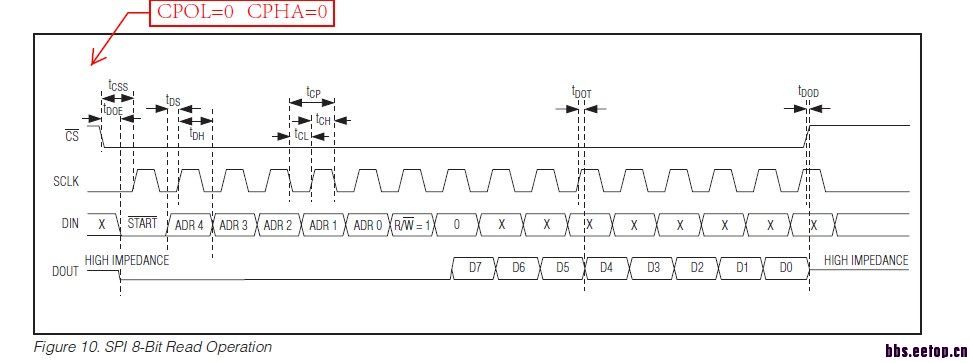

是我的从设备适应人家的主设备。主设备主要就提供给我找个时序图,通过mosi口发给我16个字节的数据,前八位是地址含一个读写状态位,后八位是数据。主要是从设备可以是被多个寄存器的地址,看了很多现有的从设备的代码,没有相关的识别地址和读写状态的。这个在从设备中应该怎么实现?你就按照人家提供的时序图,在CS为低的时候开始做0到15的计数采样,对照时序图从新排列你的数据,区分地址和读写使能,还有就是你要弄明白的人家的数据发送是怎么发送的,16比特数据发送有可能是从最高位开始发送 也可能是从最低位开始发送的,然后你去从新组合你的数据。比如计数器初始化值为十进制15,在计数器为6的时候的采样值就是对方的读写使能标识位。SPI相对比较简单, 每个公司提供的又不一样, 所以就没有固定的像你说的地址识别之类的了 。这样说了 也许你就明白了,

认真看看时序图,在start 后面,是5bit 的 address, 后面一位 r/w

就是所谓的 读写 啊

你只要 读这位的 值就 ok 。请问具体的设计流程是怎么样的呢

FPGA作为从机与STM32进行SPI协议通信---Verilog实现

http://blog.chinaaet.com/detail/35590

spi从机是否一定要有外部快速时钟clk来检测主机发过来的同步时钟sclk的上升沿或下降沿吗,在写从机代码时是否可以直接用posedge sclk or negedge sclk 就可以了?这个存在疑问,谢谢解答谢谢分享