时序约束问题

set_min_delay -from [get_pins {u6|out~57_I|combout}] -to [get_pins {u6|out~59_I|datab}] 0.4

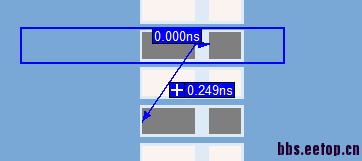

但是布局布线后的路径延时是0.249ns。

set_min_delay set_max_delay这两个约束语句具体怎么用呀?这两个约束是例外约束还是路径约束?可以起到约束掩饰的目的吗?

set_net_delay可以用来约束上面这个路径的延时吗?求大神解惑!

这个问题我也困惑过好久,set_max_delay是组合逻辑约束,是约束组合逻辑之间传输的时间,

在时序逻辑中,可以约束两个触发器之间的组合逻辑,约束完成后当查看这两个触发器之间的时序图形时,会看到组合逻辑是否满足此约束

用虚拟时钟吧

是用create_generated_clock这个约束语句吗?

类似这样的约束语句吗:create_generated_clock -source [get_pins {u6|out~32_I|combout}] [get_pins {u6|out~40_I|datac}]

那怎么约束路径延时呢?

...错看成IO了。这里只能用set_net_delay,但违规了TQ不会报Violation

set_net_delay -max -from [get_pins {u6|out~57_I|combout}] -to [get_pins {u6|out~59_I|datab}] 0.5 set_net_delay -min -from [get_pins {u6|out~57_I|combout}] -to [get_pins {u6|out~59_I|datab}] 0.4

set_net_delay的用法对吗?

set_net_delay -from [get_pins {u6|out~32_I|combout}] -max -to [get_pins {u6|out~40_I|datad}] 0.5我用这个语句也不起作用,请问怎么看命令违不违规,感觉set_net_delay这个命令不起什么作用呀,还有其他的方法可以改变布线吗?

约束不能代替设计。

我看了一下TQ report,发现我设定约束语句都被ignore了,有什么方法可以不被ignore吗?谢谢

我想,区间[0.4, 0.5]大严格了吧。[0, 0.5]试一试。

set_min_delay, set_max_delay 就可用于IO端口间的组合逻辑路径。

刚发现TQ report中,显示我设定的约束语句都被ignore了,怎么不让约束语句ignore呀?