Xilinx FIR IPcore 系数重载问题

时间:10-02

整理:3721RD

点击:

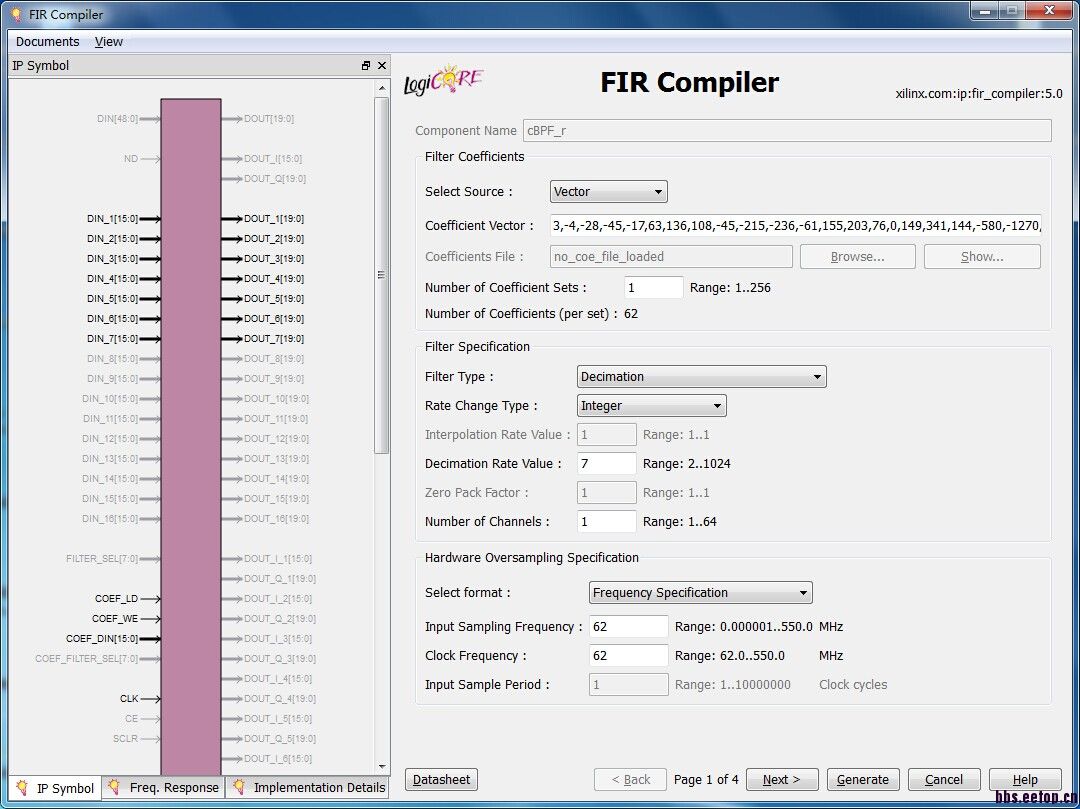

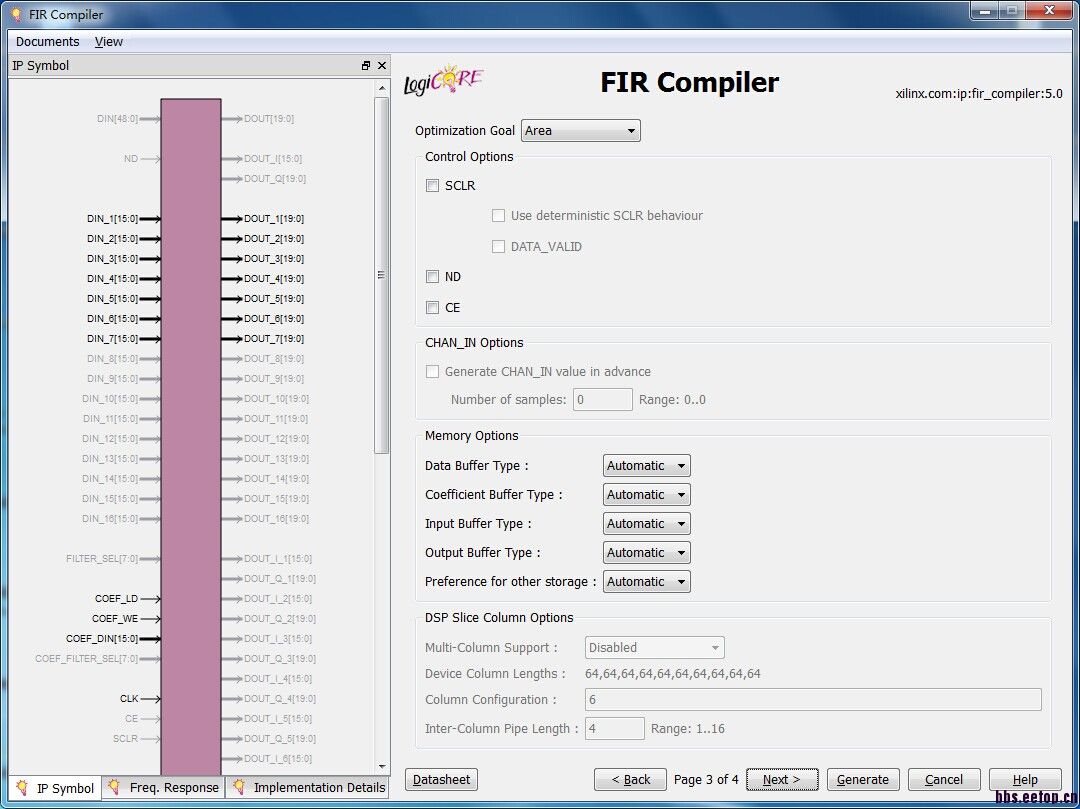

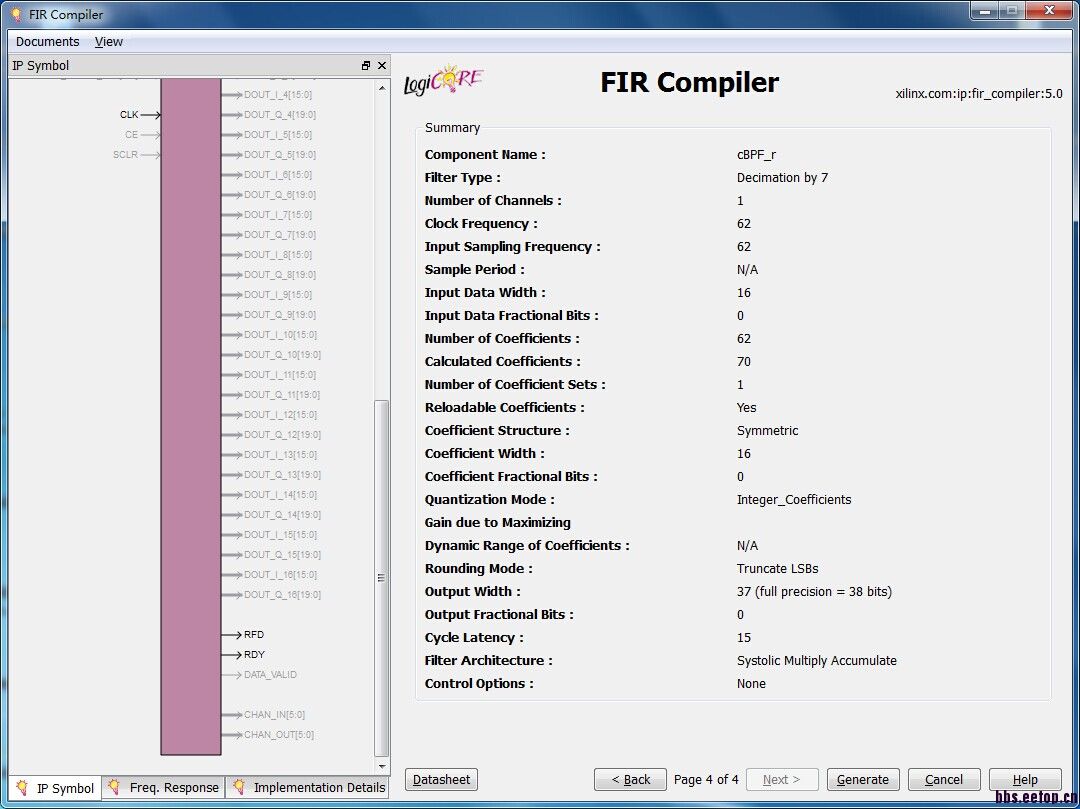

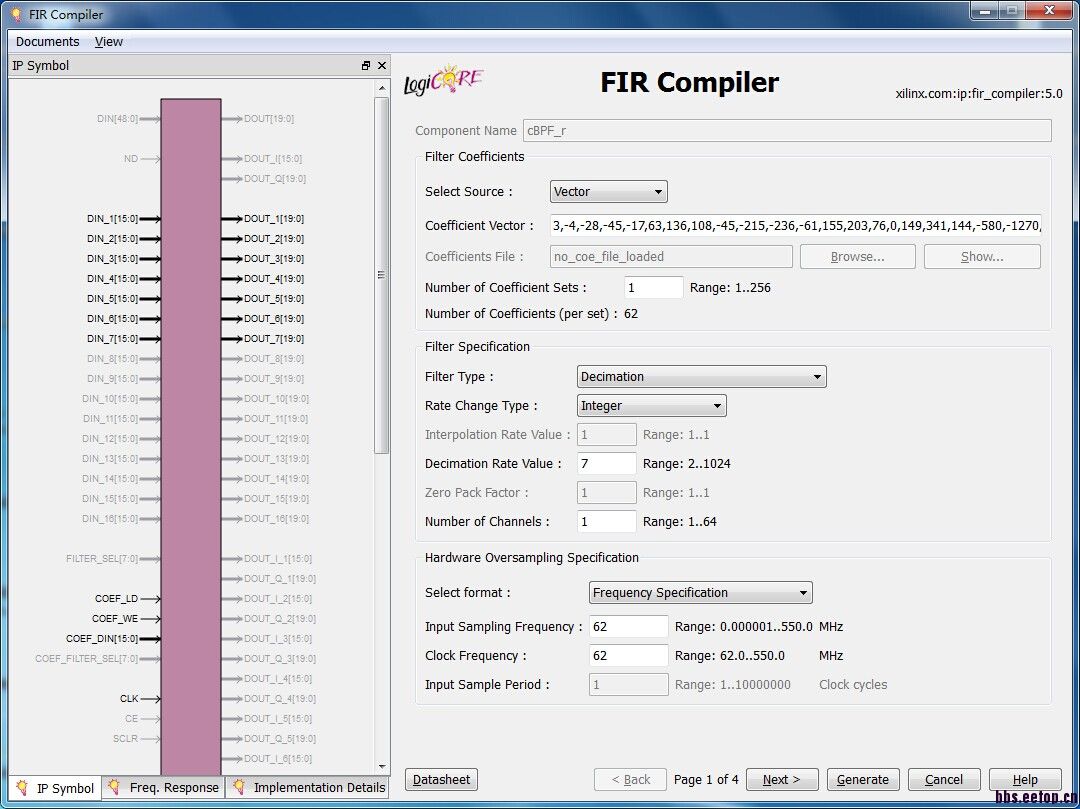

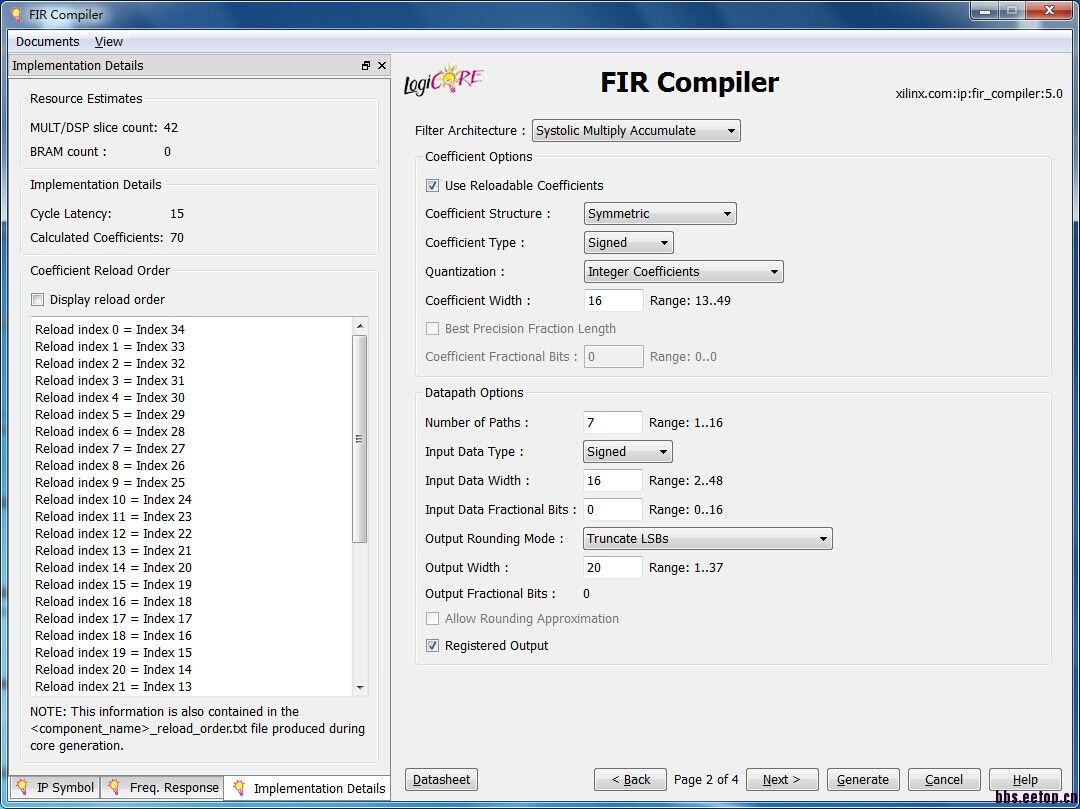

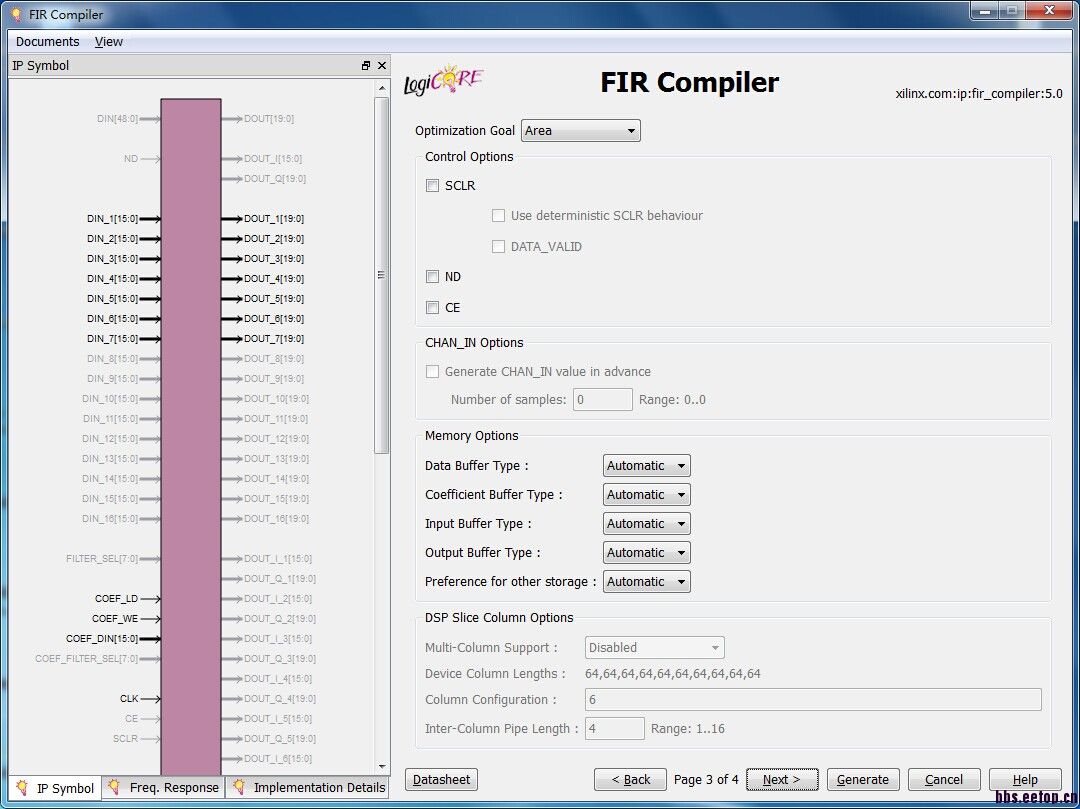

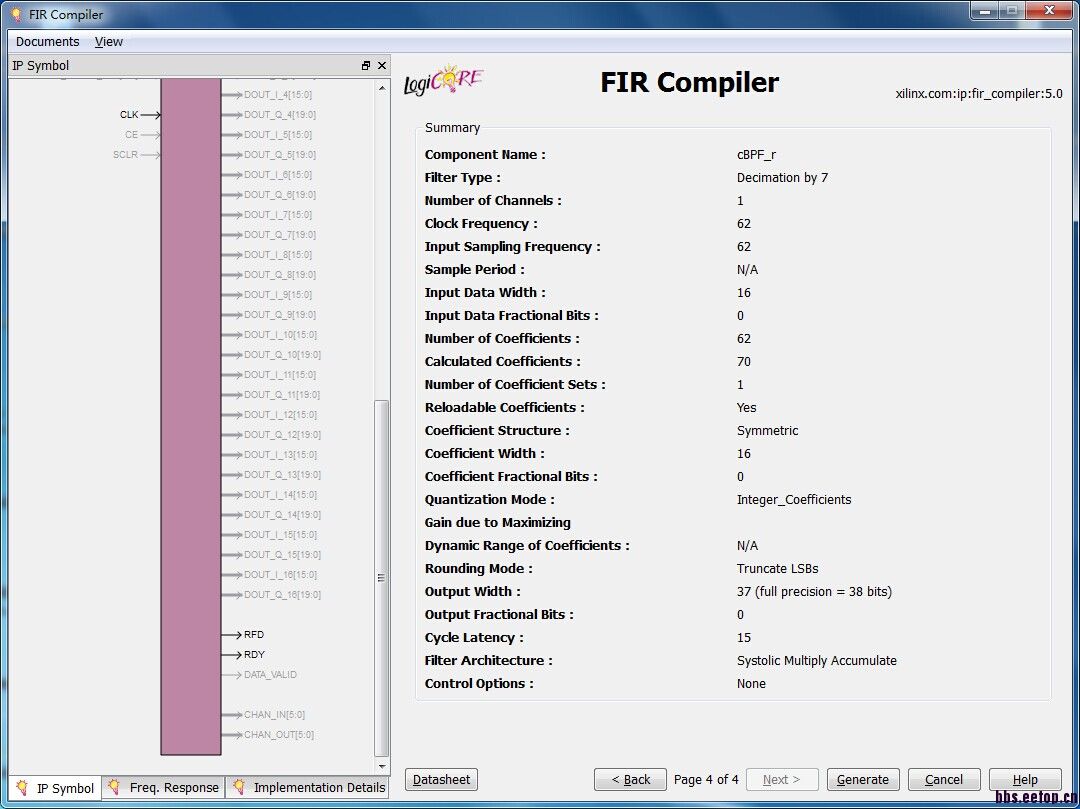

求教:本人用的ISE版本13.4 IP LogiCORE FIR Compiler v5.0

1.本人设计7路抽取滤波器62阶,系数位宽是16位

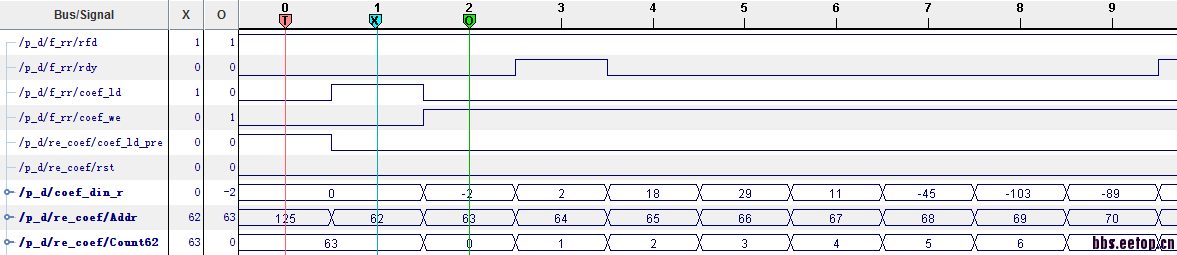

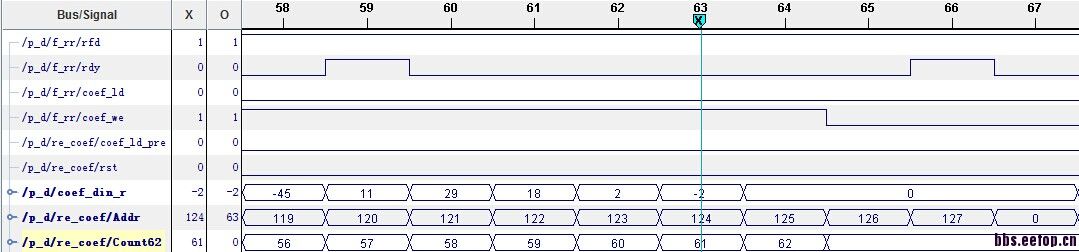

2.选择了系数重载功能124系数存在RAM中,新增了.coef_ld/coef_we / coef_din三根信号线

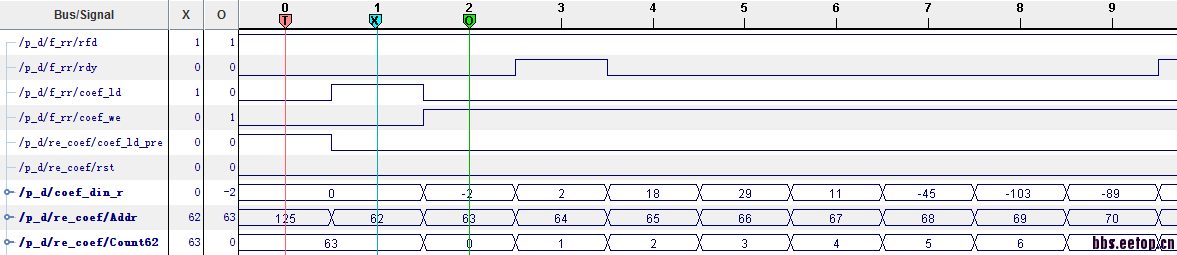

3.按照手册上的时序来加载系数,用chipscope观察滤波器不能正常工作,

不知道是哪里出了问题,请教各位一下

还有几个问题:

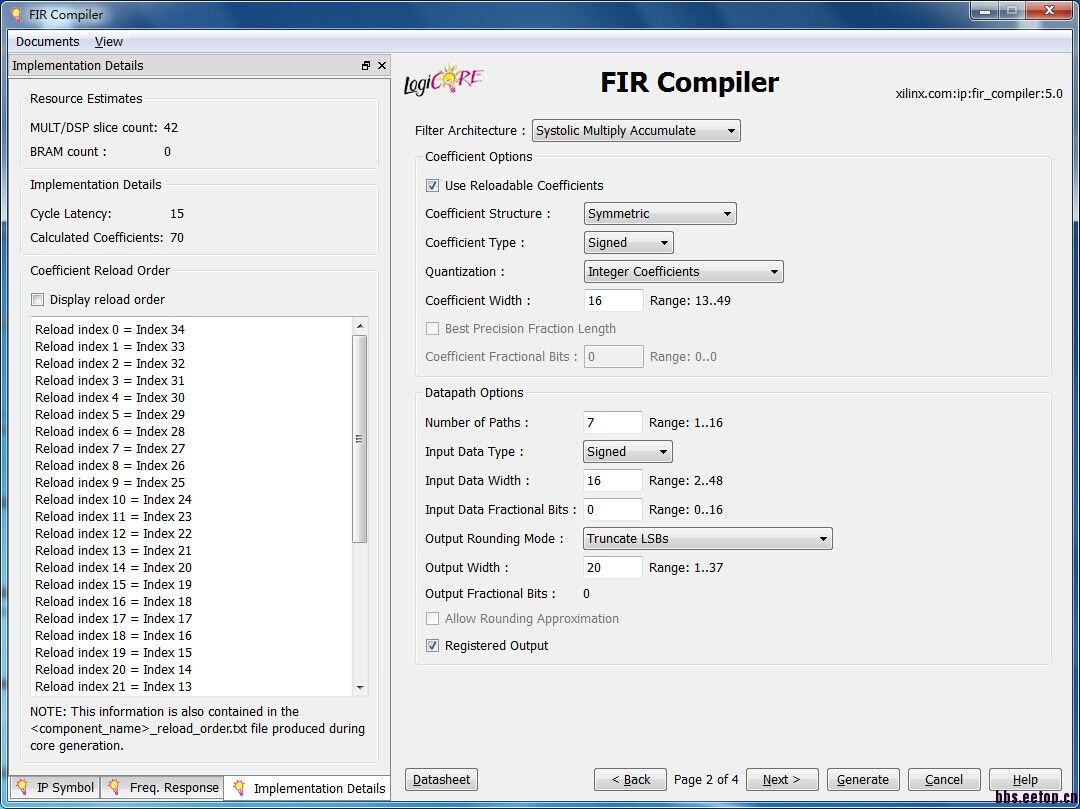

1.加载滤波器系数时,会让设定Coefficient Reload Order,对于系数对称结构的滤波器,是否按照默认就行?

2.我使用的是系数对称结构的滤波器,是不是只需要加载前33个系数就行,加载的顺序是顺序还是倒序呢?

3.coef_we脉冲的宽度是系数个数的总宽度还是总宽度加一个时钟宽度呢?

谢谢大神们的指教!很急啊

1.本人设计7路抽取滤波器62阶,系数位宽是16位

2.选择了系数重载功能124系数存在RAM中,新增了.coef_ld/coef_we / coef_din三根信号线

3.按照手册上的时序来加载系数,用chipscope观察滤波器不能正常工作,

不知道是哪里出了问题,请教各位一下

还有几个问题:

1.加载滤波器系数时,会让设定Coefficient Reload Order,对于系数对称结构的滤波器,是否按照默认就行?

2.我使用的是系数对称结构的滤波器,是不是只需要加载前33个系数就行,加载的顺序是顺序还是倒序呢?

3.coef_we脉冲的宽度是系数个数的总宽度还是总宽度加一个时钟宽度呢?

谢谢大神们的指教!很急啊

先自顶一下啊!

希望大神们的指点呢!真的是很急很急的!

大神们,大神们呢!

系数需要重新调整,we的宽度是系数宽度的总和。如果你的是对称结构,应该只要导入一半的系数的就可以了。我用的时候,选的非对称结构,是多少个系数就导入多少个数。这些IP说明文档上都有讲吧

问个问题啊,这个5.0版本的FIR核与6.2版本的FIR核对于V-6来说是不是只有AXI接口这一个不同啊?我看datasheet上发表日期都是同一天,刚看这个,谢谢啊

Thanks for the share, good information

系数多了,你要重新弄一下。最好在matlab上跑一边后再自动生成

你好,我用的IP核版本,WE的宽度只有一位啊!

我用的是复滤波,实数滤波器系数是对称的,复数滤波器是负对称结构,为了方便测试,设置IP核的时候配置的是非对称的;因为时钟和数据速率是一致的;WE信号在我的IP核设置中就只有一位,不是你说的所有系数位宽的总和! 你说系数要重新调整,是因为我的系数太多,还是顺序需要调整!

谢谢你的解答

系数没问题,已经在MATLAB中试过了,时序和手册上的一样,现在不知道是哪里的问题!不知道是不是还有其他的控制信号没有添加!谢谢你的解答

可能IP核的版本不同吧,我用的是5.0的。时序说明是WE的长度是系数长度的和,5.0的版本亲测是正确的。

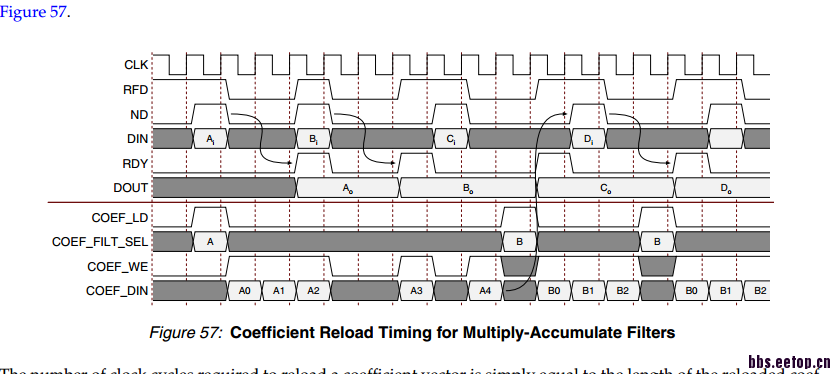

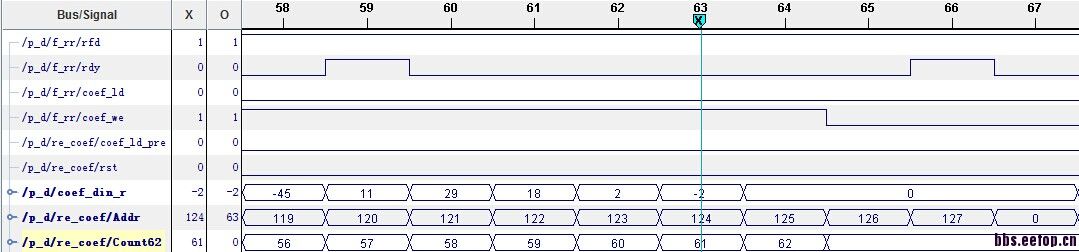

你好,我用的也是V5.0,这个是时序图