launch edge和latch edge延迟是什么意思

小弟我最近在看时序分析的知识,看到说

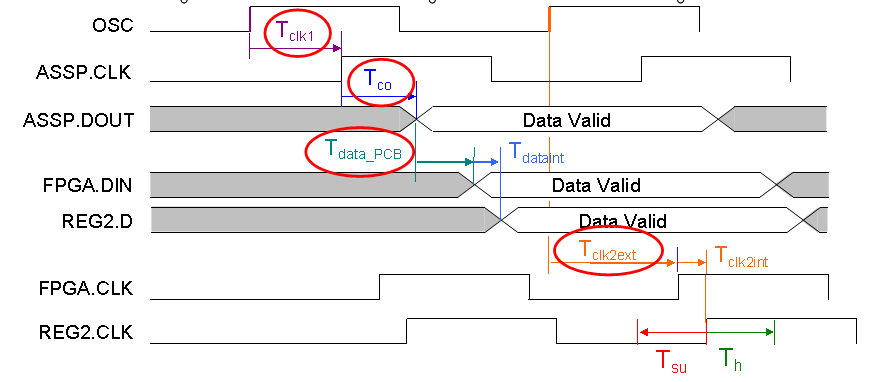

data arrival time= launch edge + input delay max + Tdataint。

想请问一下launch edge是什么意思?触发延迟的意思么?我看图上只是把上升沿的位置加粗了,这能说明那里仍然存在延迟么?就是我用篮圈画出来的地方,请会的人帮我解答一下吧。

发射沿,锁存沿

感觉就和 建立时间和稳定时间的原理一样

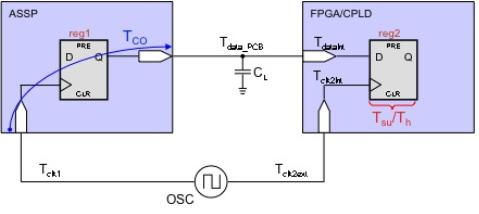

latch edge是时钟的延迟,你这个图中的latch edge是指时钟信号从振荡器OSC到寄存器的时钟输入管脚的延时。

和保持时间和建立时间一样是指,launch edge 和latch edge也是有延迟的对吧,并不像图中画的那样是瞬间从0到1,而是从0到1有一个缓慢的上升过程是么

我觉得好像不是啊,你说的那个延迟是从OSC发出到clk1端这段时间的延迟,应该是旁边的那个Tclk1。我把全图发来给你看看。

呵呵,说错了,launch edge和latch edge分别是指一条路径的起点和终点,只是一个参考时间,本身没有什么意义,latch_edge-launch_edge才有意义,通常意义上latch_edge-launch_edge=T.具体可以看看下面这个网页

http://www.cnblogs.com/inet2012/archive/2012/03/07/2384149.html

其实就是两个参考时间,分别是指一条路径的起点和终点,latch_edge-launch_edge=T;具体看下面这个网站

http://www.cnblogs.com/inet2012/archive/2012/03/07/2384149.html

谢谢你,我自己还是多看看吧。

俺是来学习的,之前听说过latch-up

我的迷惑和小编遇到的一样。不过我好像明白一些了

就是个时序分析的起点终点问题吧?