求教:Xilinx FPGA 使用AXI4总线实现DDR3控制的问题

时间:10-02

整理:3721RD

点击:

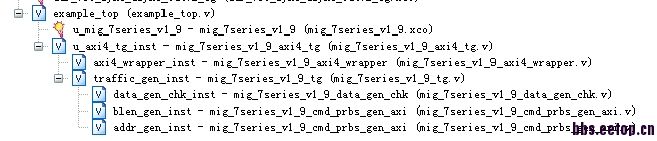

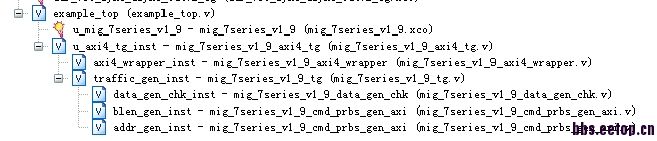

问题描述:现在我想要做的是在AXI4总线上连接两个DDR3,使得整体能实现一个数据缓存器FIFO的功能。由于小弟是十足的菜鸟,先是使用ISE生成了MIG的ip核,在设置中选择了使用AXI4 总线,然后接下来的步骤就按照ug586文档进行设置。完了之后,将IP核加入到工程,打开example_design 进行学习。通过对例子程序的学习,发现其中的traffic_gen_init和axi4_wrapper_inst两个文件好像完成了AXi4的协议控制。其中针对用户的控制量就是app_xxx的数据经过这两个文件进入IP核,然后控制ddr3,输出的变量便是ddr3_xxx。等。小弟作为菜鸟看会觉得,上面两个文件是不是我直接拿来用就行。如果不死,我要实现我想要的功能我该怎么入手呢?求大神知道?给个具体的方向,在此先谢谢了!