input delay /output delay ?

input clk ,en ,

input [7:0]AD,

output wire AD_CLK

);

wire PLL_CLK1,PLL_CLK2 ;

PLL1 PLL1(clk ,PLL_CLK1) ;

PLL2 PLL2(clk,PLL_CLK2) ;

assign PLL_CKJ3 = en ? PLL_CLK2 : PLL_CLK1 ;

lcell lcell_inst(.in(PLL_CLK3) ,.out(AD_CLK)) ;

reg [7:0]AD_F ;

always @(posedge PLL_CLK3)

AD_F <= AD ;

endmodule

以上为AD的控制采集程序 ,其中CLK为外部的输入时钟,PLL_CLK1为经过PLL后倍频的时钟100M,

PLL_CLK2为倍频后的时钟125M,

en为选择信号,选择主控时钟为PLL_CLK2 还是PLL_CLK1.

AD_CLK是输出给AD的时钟,

AD为AD进入FPGA的8位采集的数据.

其中AD的Tco参数为2ns .板子的延迟为0.5ns.

从PLL_CLK3 到AD_CLK的走线延迟为 8ns.

请问大家

1 : 如何对这个例子进行约束 ?

2 :如果要对AD进行 input delay 约束应该怎么约束呢?

3 : 如果进行output delay 约束该怎么约束呢?

4 除了输入clk外,还需要约束别的输入信号吗?

如果是FPGA应用,如果是同步设计,需要约束。(看起来你这个设计不是同步设计,所以这些可以忽略,)

1. clk,输入时钟约束。如果是ISE,则会自动计算PLL之后的时序关系。如果不能软件推算,那么就需要creat内部时钟,约束内部时钟PLL_CLK1和PLL_CLK2.

2. 管脚和时钟关系约束。en, AD,AD_OUT等等。

最后,貌似这个设计不是全同步设计,所以是不是设计有问题。如果设计就一定是全异步的话,那么这个模块的信号可以false path掉,不分析时序。

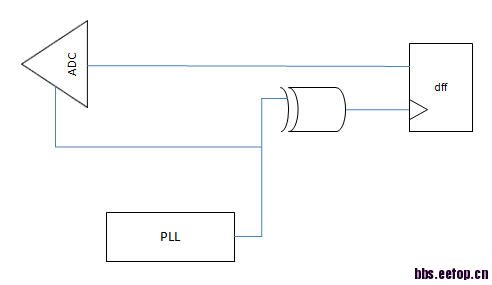

通常會作正反向clock的選擇來latch ADC的output

是同步设计的,采集的AD数据用pll_clk来控制,同时处理后的数据也是采用pll_clk来控制。

而ad_clk时钟也是pll_clk来产生的。

我在想如果加入 input max delay /input min delay 应该怎么设置?

可以将的详细一点的

感觉应该设两个时钟,一个虚拟adc_clk,用在adc那边产生AD,这个虚拟clock相对pll 延迟8ns

另外一个就是AD这边的PLL_CLK3. (直接取频率更高的125M)。然后AD的input_delay用2.5ns

OK,谢谢你了。呵呵,我来尝试一下,以前我没有加虚拟时钟约束,参考时钟老是会错误,就只能用 * 来代替了

就是pll_clk3到ad_clk的延迟太大了。 不知道具体怎么设好。

等高手出现

clk,输入时钟约束。如果是ISE,则会自动计算PLL之后的时序关系。如果不能软件推算,那么就需要creat内部时钟,约束内部时钟PLL_CLK1和PLL_CLK2.

顶起。等待高手出没

如圖

一般會用design去cover這種路徑的timing,

這樣做只須把ADC output 到 FF 的 data path bus skew盡量壓小就可以了。

BR,

Jarod

这个做法不错。从设计上减少了半个周期的skew

需要设input delay 的只有en,相关clock是 clk,设output delay的相关clock是PLL_CLK3,具体怎么写看pt就知道了

可以详细的说一下吗?怎么设置? 怎么corver?

pt ? 在FPGA中吗?

这个模块貌似不是同步时钟电路,时钟的输出受使能信号控制,而且时钟不是作为控制,而是输入,你可以试试将其综合后看看门电路的结构,就应该很明了了吧

就是可以選正負緣sample data。

对的,这就是一个控制AD采集的例子,FPGA提供给AD时钟,并且用这个时钟来采集数据,我想知道的是应该如何约束,您可以说一下嘛?

那么 需不需要设置 input min/max delay 呢?

一般在synthesis的時候不加任何min delay/max delay,出來的結果,bus skew不會差很多,除非placement的距離差很遠。

所以只需在post STA確認 bus skew是否在可以接受的範圍就可以了。

确认这个地方要用门控时钟?

既然不是同步电路,就不需要约束啊,设置为fasle path

但是 因为有的时候 比如硬件人员为了布线方便,就把AD的某一位引脚打了过孔,而在高频的时候,必须要考虑的,你遇到过这问题嘛?

这个要考虑功耗了,如果要考虑,最好加上

两个不是同一个时钟嘛?不需要设置嘛? 比如我有8个AD,每个相位相差45度的方式,

在作broad design時通常是讓bus的長度與走線盡量一致阿。

不這樣做的話,那應該要先作broad level simulation,

看broad上的造成的bus skew是否過大阿,再用FPGA裡作補償吧。

这个有用啊