遇到一个奇怪的问题,求解答!

时间:10-02

整理:3721RD

点击:

我用FPGA驱动LCD1602,按手册,每次写LCD之前,要读LCD忙信号,我把读到的忙信号放变量K 里,供状态机判断(如果K为高,就说明LCD忙,然后状态机停留在本状态,直到K为低).现在遇到个奇怪的问题:向LCD连续写数据,很快LCD就不再有任何显示了,必须复位或者重启才能正常,所以怀疑是K导致,我就把这个变量K引出来放在空余管脚上,想观察状态,结果,程序没做任何改动情况下,再怎么连续发数据,LCD都能正常显示了,接着我又把K从管脚上取消掉,问题就又依旧了,实在很奇怪,你们曾遇到过类似问题吗?有可能是什么导致的呢?

变量K是什么类型?REG,WIRE?驱动它的信号来源是怎样的?有没有高阻态?

是REG类型,奇怪的是,为什么把这个信号引导出到管脚后,就没再出错了,很想知道因为什么导致这个问题

这个信号综合后应被优化掉了,不存在这个寄存器了。

但是如此你放它到输出PIN,这个寄存器会被保留。 或者你设个保持它不被优化的约束,估计上板也会正常。

总的来说,你代码写得可能健壮性不够才导致问题,不介意的话把相关代码放上来看看。

上代码呗

在RTL VIEWER 里有K,没有被优化掉,同时LCD是能够正常显示的,只有当连续不断(间隔大约100MS)给LCD写数据,才会显示出错,如果间隔时间比较长,LCD还是能正常显示的,无意间我吧分析综合设置里的最优技术,从平衡修改为区域,问题解决了!无论发多快数据,LCD都能正常显示.把K引出来,也是因为改变了chip planner,才正常的.

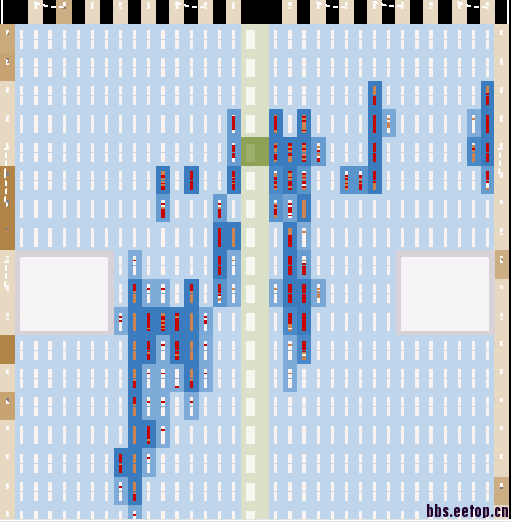

平衡优化时的 chip planner

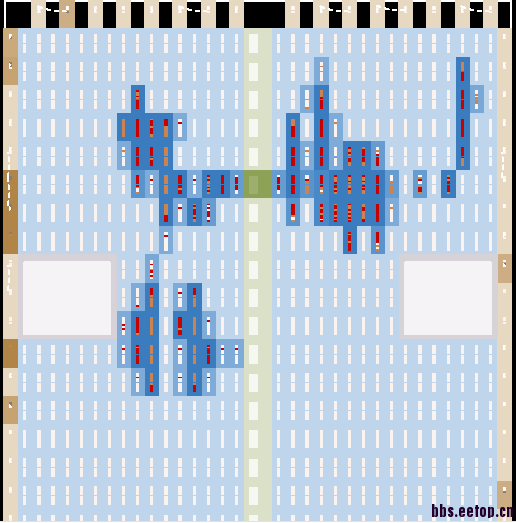

区域优化时的 chip planner

这个问题是否就是时序导致的呢?

时钟频率是多少?有timing slack报告吗?

这个问题更多像是状态机健壮性不够,进入了死状态,这方面好好看看。

时序问题的可能性很大

不应该是用时序约束控制让编译器自己去布局布线的么?