一个时序优化的问题。

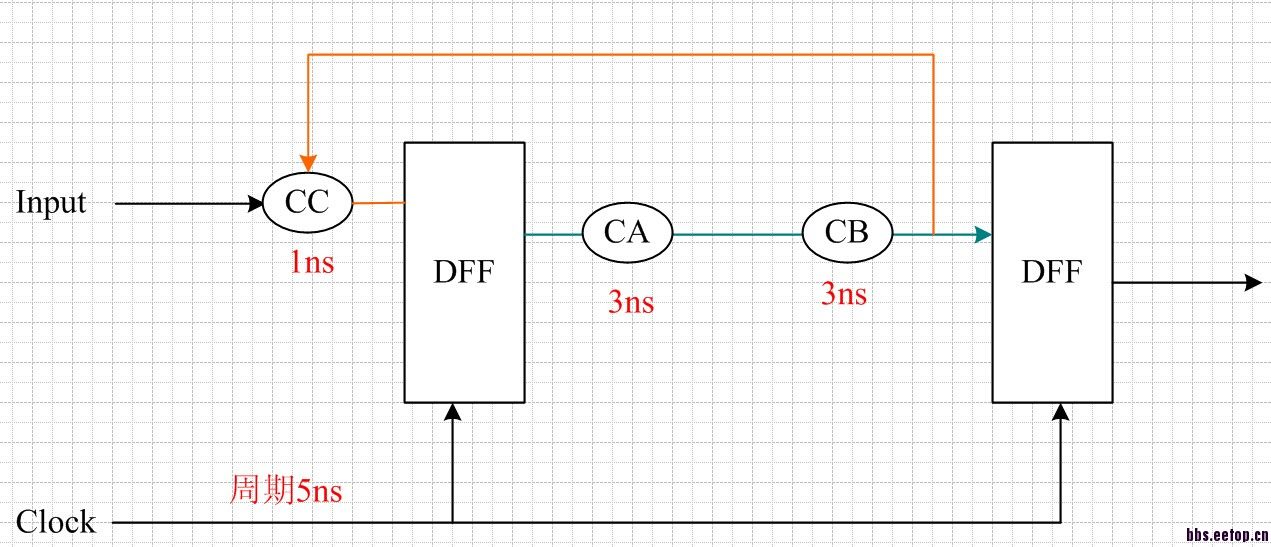

如图,两条path的timing 都不满足。

要求修改rtl,在不影响功能的前提下,满足时序。

我觉得这个是无解的。有高手知道吗?

要改RTL总是有办法的

求大神指点迷津啊!

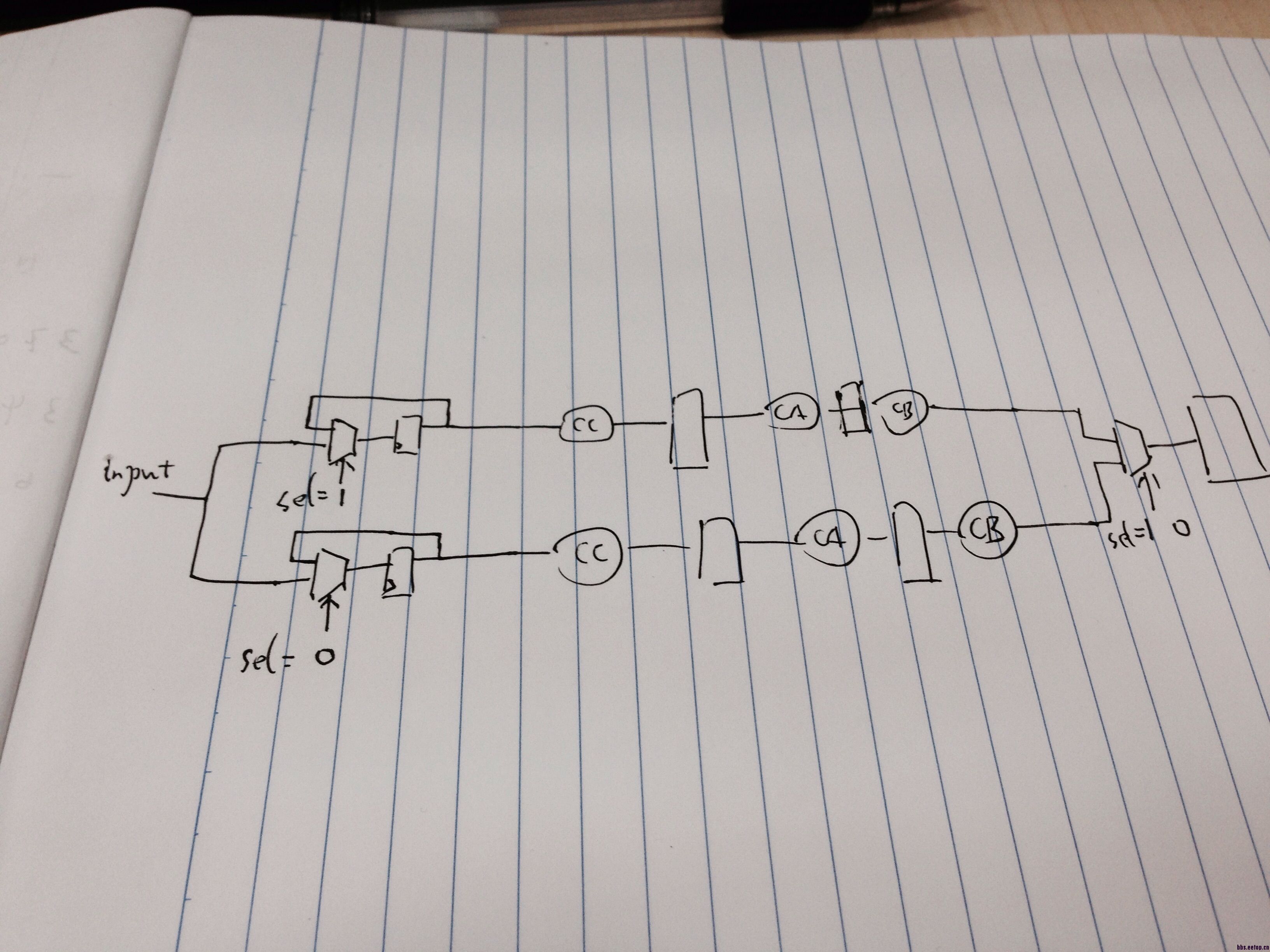

我不是大神,因为我不知道你前后逻辑,一般会想到组合逻辑用寄存器切开,但是会两个周期,这样有个问题就是input的输入速度和output的输出速度会有变化。,我觉得可以把你那部分逻辑a(叫a吧)复制一下得到b,就是并行,然后input的数据5ns一个给a,下一个5ns给b,然后输出同样合并一下。

没看明白啊。橘黄色这条path,3段组合逻辑之前有先后关系。要1拍之内完成。

CA和CB之间加一级寄存器行么

降速吧

学习学习

11111

一般有两种处理方式:

1. 流水线方式,也就是在逻辑CA和逻辑CB之间插入一级寄存器

2. 逻辑优化方式,也就是将部分CA、CB的逻辑前移一级寄存器,这种方式在布局布线时常用本来插了寄存器要两个clk才能处理完,但是用相同的两部分逻辑,这样可以做到1个clk处理完

这种loop的电路,插FF肯定是不行,只能想法优化CA和CB的实现了,特别是CA->CB这条path.

还有就是看看是不是CA->CB->CC这条path里,有没有假的path,比如真实的path是CA中间的某个信号->CB->CC, 而不是必须是CA的最终结果->CB->CC。

还有就是尽量把CB->CC的反馈信号放在最接近FF-D端的位置。学习了

你的这个并行实现的思路挺不错哈。

但是第一个DFF的loop logic就不对了。

有道理。这是瑞芯微的面试题

我觉得是个奇葩

loop逻辑又不输出,只要满足什么样的输入得到什么输出,并且时序满足就行了把。

不是的。假如CC逻辑是加法器,CA是加1,CB是加1。

假如input数据流是:1,2,3,4,5...一拍一个数据。

那么DFF1的输出是:0,1(input+0),5(input 2 + 3),10(input 3 + 7)。

那么CB的输出就是:0,3(1+1+1),7(5+1+1), 12(10+1+1)。

如果在CB到CC之间加一级DFF,cbreg:

那么DFF1的输出是: 0,1(input 1+0),2(input 2 + 0),6(input 3 + 3),8(input 4 + 4)。

那么CB reg的输出就是:0,0, 3(1+1+1), 4(2+1+1), 8(6+1+1)。

完全不一样了。那样是不对,想简单了,现在有点事我待会再想想把两路加些逻辑关联起来看看

不知道想的对不对。

复制逻辑,然后交叉循环,即:上面逻辑的CB给到下面逻辑的CC,下面逻辑的CB连到上面逻辑的CC,然后最后通过一个二选一这种办法搞不定,插了寄存器怎么也得不到下一个时刻数据,只能再想想别的了

不加寄存器,把寄存器移动到AB之间

两个DFF之间的timing满足了,但是第一个DFF的loop还是不行。除非input输入的数据不是5ns一个。要不我是没办法了

这个思路不错啊。我仔细算了一下,时间上还是来不及。难道得复制3份?