Altera uniphy_ddr3_controller 错误

时间:10-02

整理:3721RD

点击:

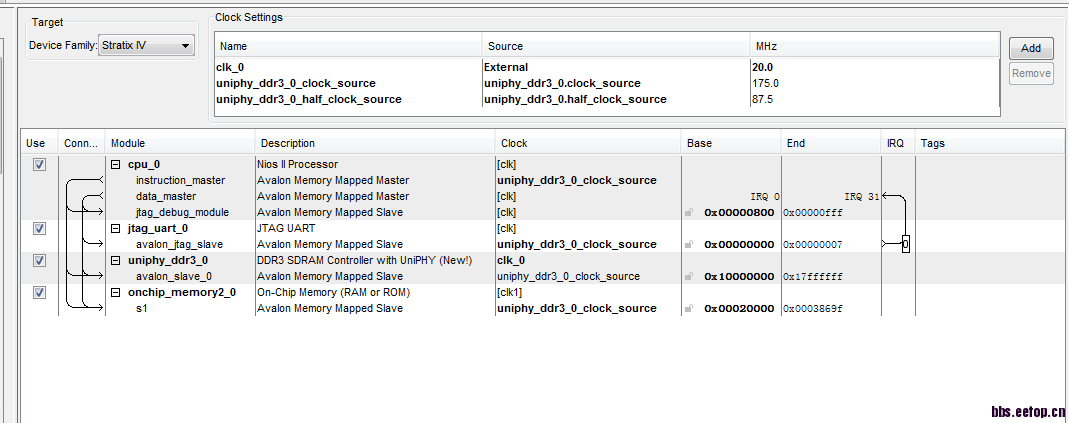

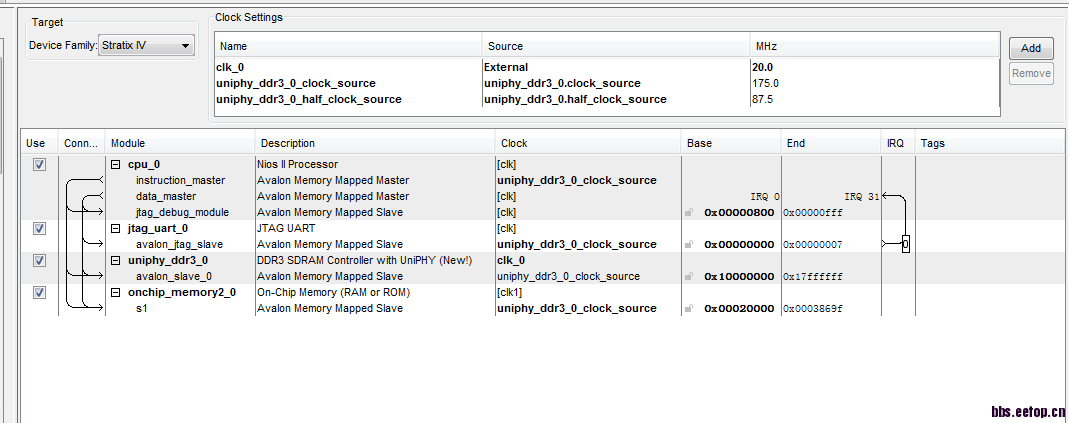

用quartus 10.1 搭建一个DDR3的小工程,其sopc系统如下图所示,

SOPC系统生成后去做系统仿真是没问题的,但是在start Analysis & Synthesis 时,最后将要完成的时候,会出现如下错误,

Error: Termination logic block atom "uniphy_ddr3_0:the_uniphy_ddr3_0|uniphy_ddr3_0_controller_phy:controller_phy_inst|uniphy_ddr3_0_memphy_top:memphy_top_inst|uniphy_ddr3_0_oct_control:uoct_control|sd2a_0" uses SERIESTERMINATIONCONTROL port, which must be connected to SERIESTERMINATIONCONTROL port on an output buffer atom

Error: Termination logic block atom "uniphy_ddr3_0:the_uniphy_ddr3_0|uniphy_ddr3_0_controller_phy:controller_phy_inst|uniphy_ddr3_0_memphy_top:memphy_top_inst|uniphy_ddr3_0_oct_control:uoct_control|sd2a_0" uses PARALLELTERMINATIONCONTROL port, which must be connected to PARALLELTERMINATIONCONTROL port on an output buffer atom

还请搞过DDR的大哥大姐们,看看这个问题该什么解决........

SOPC系统生成后去做系统仿真是没问题的,但是在start Analysis & Synthesis 时,最后将要完成的时候,会出现如下错误,

Error: Termination logic block atom "uniphy_ddr3_0:the_uniphy_ddr3_0|uniphy_ddr3_0_controller_phy:controller_phy_inst|uniphy_ddr3_0_memphy_top:memphy_top_inst|uniphy_ddr3_0_oct_control:uoct_control|sd2a_0" uses SERIESTERMINATIONCONTROL port, which must be connected to SERIESTERMINATIONCONTROL port on an output buffer atom

Error: Termination logic block atom "uniphy_ddr3_0:the_uniphy_ddr3_0|uniphy_ddr3_0_controller_phy:controller_phy_inst|uniphy_ddr3_0_memphy_top:memphy_top_inst|uniphy_ddr3_0_oct_control:uoct_control|sd2a_0" uses PARALLELTERMINATIONCONTROL port, which must be connected to PARALLELTERMINATIONCONTROL port on an output buffer atom

还请搞过DDR的大哥大姐们,看看这个问题该什么解决........

这个提示,说明你得自己在代码,或者qsf中手动定义SERIESTERMINATIONCONTROL和PARALLELTERMINATIONCONTROL.

rdn rup赋值了吗? 没有赋值会报错误这个错误的

没有加约束,在tcl script里面运行一个叫*******_pin_assignment.tcl的文件就可以了。

赋值?在还没有编译之前就要对rup 和rdn 进行赋值?这两个引脚应该是连接校准电阻的吧?应该怎么样去赋值,不太很理解。不可能直接让rup赋值为1'b1 ,rdn赋值为1'b0吧?能在详细点吗?谢谢。

我已经运行这个tcl 脚本文件了,但是在编译的过程中还是报这个错误。很纠结,不知道该这么去处理了...

你好,你说的这一点我第一次接触,不太很明白。能否说的在详细点或者举个类似的例子?非常感谢!

是不是你的引脚设置有问题啊,它们的设置需要遵循许多规则的!

set_instance_assignment -name INPUT_TERMINATION "PARALLEL 50 OHM WITH CALIBRATION " -to your_port

set_instance_assignment -name OUTPUT_TERMINATION "SERIES 50 OHM WITH CALIBRATION " -to your_port

了

Good