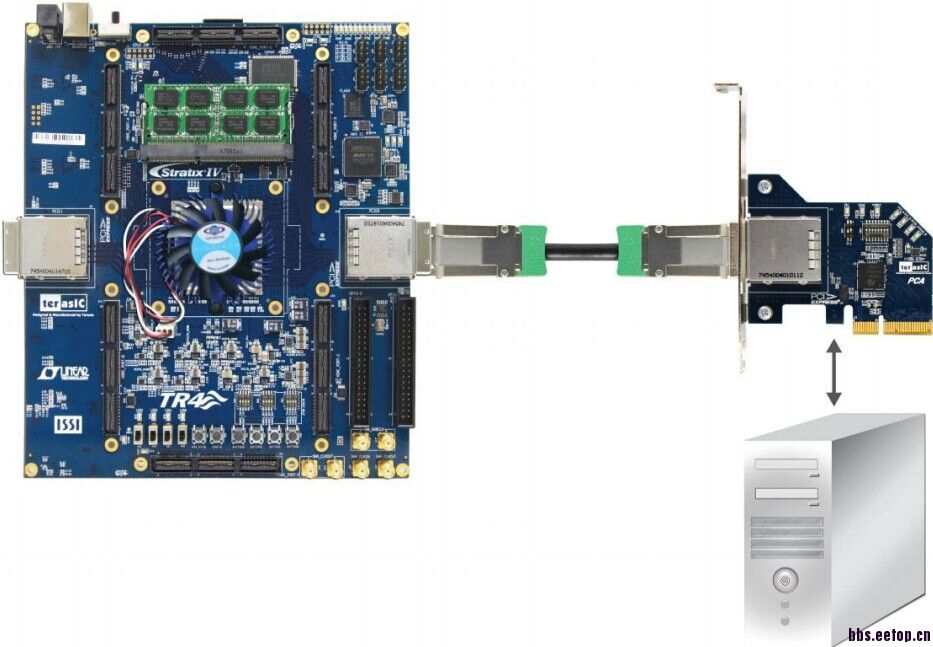

PCIe这样搞好像也不错嘛

时间:10-02

整理:3721RD

点击:

王哥,这是什么啊!之前说搞个pcie,没想到你没带我们搞,自己偷偷摸摸在搞啊!

确实很不错!

这是被人的板子,我是觉得这个方案还是挺不错了

连线可以用MiniSAS

雷电接口嘛?成本如何?雷电好像用的是MiniDP接口吧?

这样弄也不错,你是跑GEN2还是GEN3?

再长一点也没关系的,已经经过这样的转换了,电学性能的损失已经存在,再长一点关系不大,在半米内应该性能都还不错,不行弄30CM的。

有更好的方式就是直接跑PCB板,就是不存在线缆了,一个额外的小卡,直接把这个接口转为PCIE的接口,然后插入电脑PC插槽,Synopsys有这种卡卖。

去年想过要这么搞,被否了,换了别的方式。还是不甘心,想接着弄,呵呵

早就有了 pcie x1 的软连线。 GEN2 看来很难支持, GEN3 就更不可能。

我们的速率不是太高,只是为了怕以后数据会增加。目前使用的是外购的PCIe x1,出现瓶颈了,所以希望升级到x4,Gen1就可以了,但是希望兼容Gen2,所以上述方案非常适合,因为该电缆和PCA适配卡支持Gen2.

你提供的方案应该是不太适合我们的项目,因为我们的数据板是需要插在我们系统的背板,数据从数据板传到DAQ卡上的。现在想在数据板上的fpga中实现add-in模式的pcie接口,通过电缆连接pcie适配卡。

被否的原因是什么?后来换成什么方式了?

无法回复你?

不能回复你?!

to coyoo :我也奇怪没法直接回得你的贴子。

软线确实存在很多限制,做工好些的跑GEN2还OK,跑GEN3直接没戏。

这是什么意思啊