两个AD芯片时钟不同源,FPGA输入的两路数字中频应如何处理?

时间:10-02

整理:3721RD

点击:

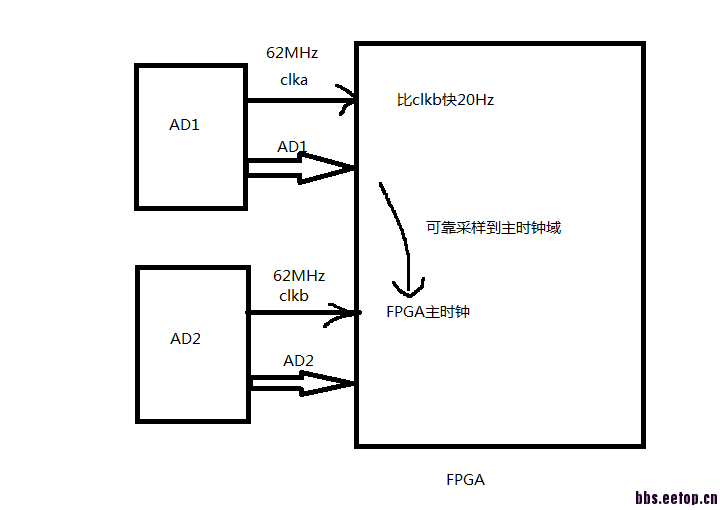

板上有两个天线,两路模拟中频A和B,经两片AD(时钟不同源,采样时钟均为62MHz,数字中频均为15M)采样后给FPGA,各自的时钟也分别给FPGA,但是A的时钟clka比B的时钟clkb稍快,大概快20Hz。FPGA的主时钟使用B的62MHz。扩频通信,需要对信号进行连续跟踪(卫星导航)BPSK,码率10M,数据率500bps。涉及到跨时钟域采样的问题,请问各位大牛都是如何处理这种情况的?

我们使用了一个FIFO,用clka控制写入,用clkb控制读出。使用其“almost full”和“almost empty”来控制读写信号。“almost full”时丢掉一个写入数据,“almost empty”时保持读出数据保持上一值。由于clka比clkb快20Hz,因此每隔50ms会丢失一个数据,请问这种情况会影响信号的频谱吗?现在的表现是信号不能稳定跟踪,环路不稳,误码较高。请各位大侠解惑支招出主意,有哪里表述不清请提问,需要测什么我配合。不胜感激!

自己顶一下

用各自的时钟做信号处理,或者避免丢失点两侧的信号做频谱分析,个人感觉即使是用丢失点两侧的信号做频谱分析,对频谱的影响也可以忽略。

信号不能稳定跟踪,环路不稳,误码较高----不明白是什么意思

两个fifo输入时钟用各自的,输出时钟都用fpga内部同一个时钟

应该会引入杂散吧