FIFO级联问题(自己代码问题,几个模块搞混了)

时间:10-02

整理:3721RD

点击:

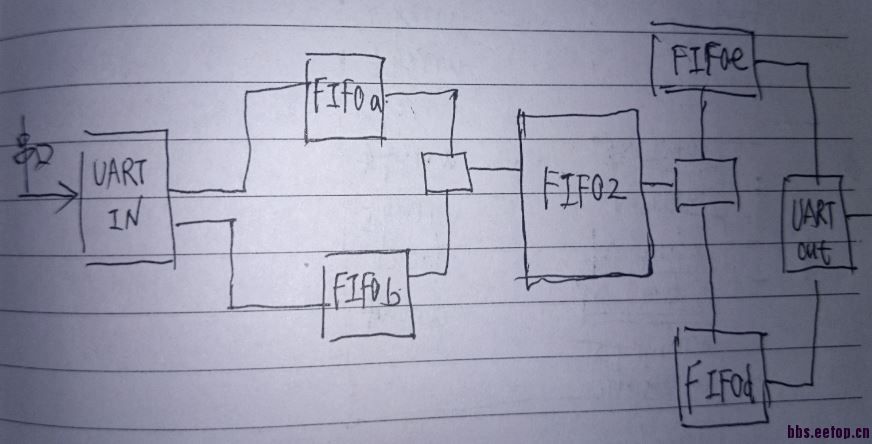

做了5个FIFO,2个前置FIFOa FIFOb,一个中间的大FIFO2,两个后置FIFOd,FIFOe 串口进数据,对应的帧头进对应的前置FIFO,前置FIFO写满后传给中间的大FIFO。

之后大FIFO读出数据给后置FIFO,也是对应的数据放到对应的FIFO中,通过另一个串口发出。

如图:

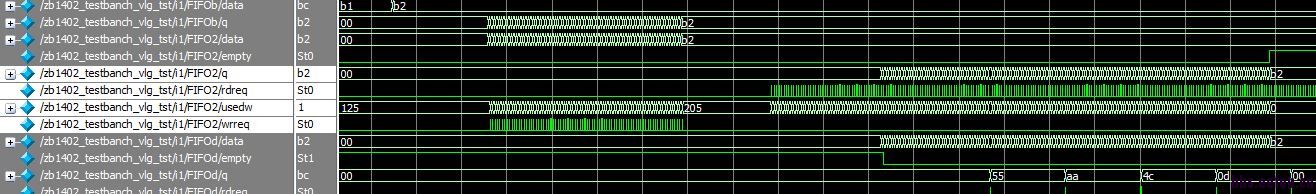

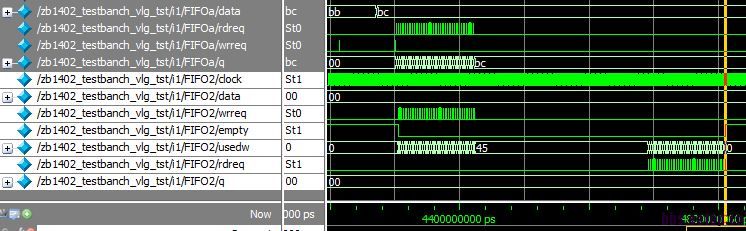

我写好后功能仿真起初是通过的,但是添加了别的模块以后出现了FIFO2读不出数的现象。FIFO级联之间只有一个8位寄存器

做缓存。

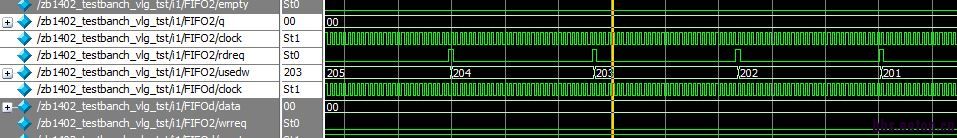

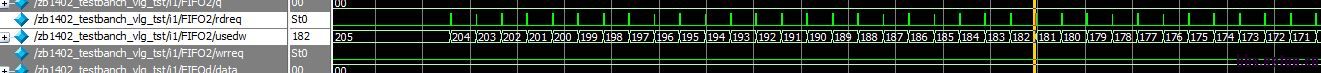

具体情况是,FIFO2的读使能有,usedw也在减少,但是q引脚没有数据变化,过了一段时间以后又出来数了,

不知道有没有人遇见过类似问题。实在不明白怎么回事。

简单地说是单独仿真是能通过的,加了其他模块,它通不过了,现象是读不出数,usedw还在减少。

所有FIFO都是使用系统CLK做读写时钟。FIFO的写请求和读请求都是一个周期的高电平。 恳请大家帮忙看看,感激不尽。

今天尝试的时候发现,第一级FIFOa的数据看似写进去了,但是读的时候没有数。将FIFO2改成单口RAM也是同样的效果,不知道有没有大神遇到过类似现象。

问题发现了,我自己每个模块的写了几种方法,捏合的时候,模块版本没陪对,导致有的逻辑不起作用了,唉,菜了。

哎呀,图片删不下去了。

不知道有没有做过FIFO级联的大神,是不是级联的时候需要做一些特殊处理?

fifo有数据吗?怎么看前面没出数据的地方empty是高的啊。读fifo前有checkfifo的空满状态吗

fifo不空的时候,给了读使能,读出来的就是单元里面的数据,感觉没有数据的话,可能是数据没有写进去吧。

过了一会数据出来了,说明刚才写进去的数据排到了后面,FIFO是先入先出的,很可能是上一次没有读完。

fifo wr 和rd的enable信号是怎么操作的 ? lz能说一下么 ?

看起来是有数据的。是从前一级缓存FIFOa和FIFOb写进去的。我的几个不想关的模块,单个仿真是好用的,和在一起就出现了这样的情况,我在想是不是因为代码书写不规范导致综合出了问题。

clk是系统clk,wr和rd都是一个clk的长度,clk的上升沿在wr和rd的中央