为什么Xilinx FPGA器件中要分几个时钟域呢?

不过好像这个“时钟域”和什么“跨时钟域设计”中的时钟域不是一个概念啊。求解。(上面只是一个器件资源,时钟信号都没有啊)。

这么分一个区域有什么用呢?

有bufh bufr的概念,你搜搜看

FPGA一般分为几个时钟区域,每个时钟区域通过缓冲器驱动

浏览一下器件的handbook就会发现FPGA内部提供了不同的时钟buf资源,全局时钟GCLK可以驱动到FPGA内所有的触发器,提供低漂移的时钟信号,还有一种叫区域时钟RCLK仅仅驱动到一小块区域,这种时钟资源能够提供低延迟低漂移的时钟信号,用于相对高速的逻辑,DDR3 ip core一般就使用这种信号。

另外,时钟信号是看不到的,时钟的参数可以在静态时序分析后得到

希望对你有帮助

时钟资源是不是就是一些缓冲器啊?时钟信号是来自片子外面的吧?

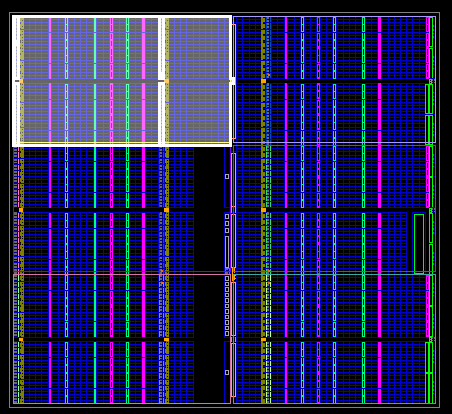

当芯片面积小的时候,所有的资源都能被访问到,从一点到最远一点的延时也能忍受; 但是随着时钟频率越来越高,周期越来越小,同时设计复杂度加大,从一点随意访问另外一点的挑战越来越大,如时钟内部走线SKEW,驱动能力,复杂度也增大,其它元素也面临同样的问题,那将之拆成若干部分成为种方法,如BANK,BUFR的引入。

等到了V7,发现这样还不够解决问题,又引入了SLR概念,三个BANK构成个SLR,里面的结构就如同一块V6芯片了(如上下部分、左右部分概念同样有),而一块V7又有几个SLR,SLR间有专用走线,如果跨越,会有较大的时延,一般相关的设计最好都在同一个SLR和BANK里完成。

FPGA内部时钟也要兼顾几个有关时钟的关键参数:延时、抖动、偏移。

需要一些办法在这些参数之间平衡。

所谓鱼和熊掌难以兼得。

我说一下我的理解,不知道对不对啊。是不是从一个时钟域进去的CLK信号控制本时钟域的ff时延迟比较小,但是控制其他时钟域时,延迟比较大?

但是FPGA不是有全局时钟资源吗?(一般设计的时候不是都用全局时钟资源吗?)

正解!