EDK自定义IP核,黑盒,在逻辑中用ISE的FIFO,如何在PlanAHead下综合

时间:10-02

整理:3721RD

点击:

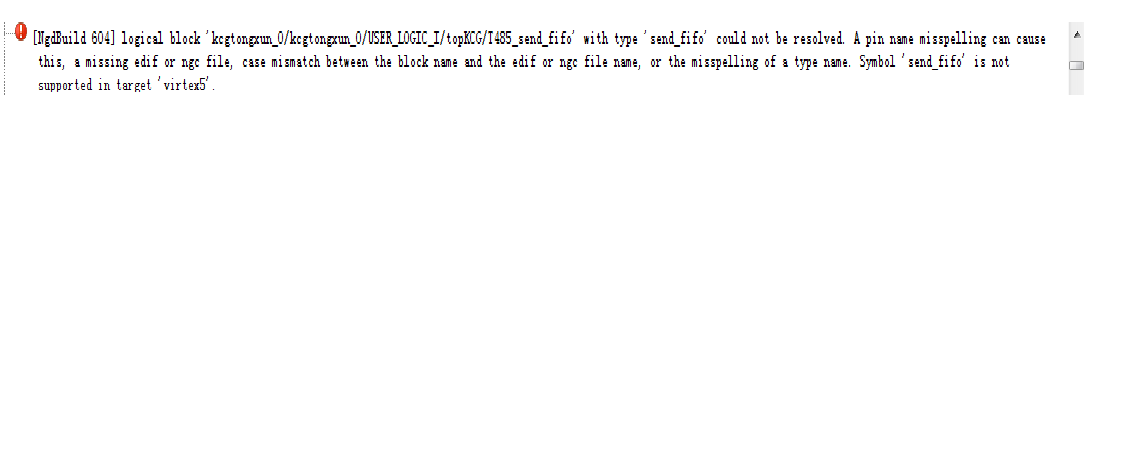

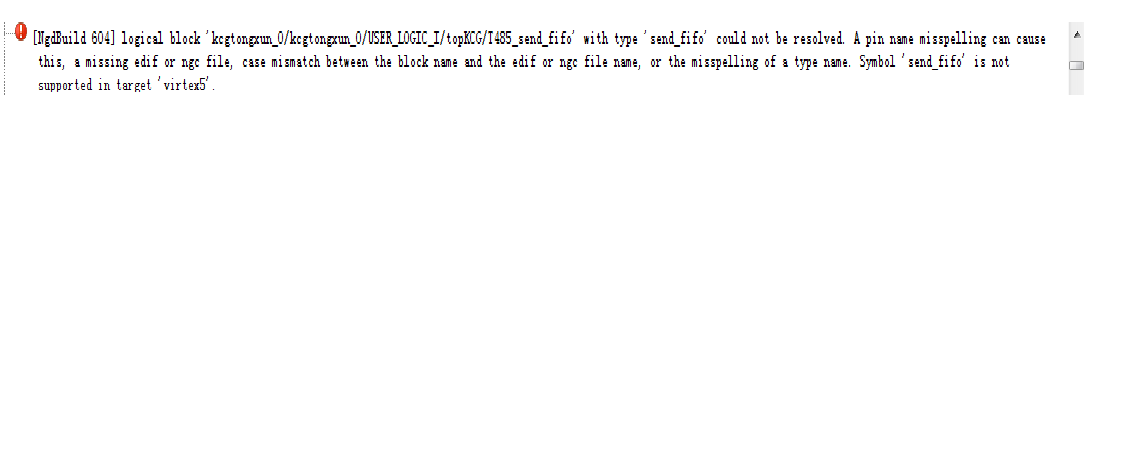

使用Xilinx V5系列的FPGA,在EDK环境下自定义一个黑IP核,逻辑由ISE下验证生成,用到了FIFO,在PlanAhead下对这个黑盒进行重构,如何把ISE使用的FIFO编译进去,错误提醒如图所示,望得到您的帮助,谢谢!

问题已解决,FIFO使用时,在PlanAhead下没指向。

能具体说明一下如何操作的么? 我也遇到了类似的问题,在Planahead12.2中错误提示类似,在planahead13.4 综合时就报错说找不到核的primitive。谢谢。

把这个IP CORE的网表文件(应该是.ngc)也导入到planAhead中即可,前面代码中调用的只是个黑盒。

这个核和这个NGC文件在ISE中就可以综合和实现。但我在planahead中的sources view中导入和删除该核的NGC文件 ,都报同样的错误。我觉得NGC文件没有问题但感觉在planahead中没有起到作用,不知道为什么。

我在中间有个步骤添加IP核的.ngc文件后,这个问题就解决了,没有遇到过出现缺少其他文件的错误

最好的解决办法就是上xilinx的官网,按照错误号找相关的解决办法,我后续遇到很多问题,百度 谷歌什么的都白扯,还是官网里面的资料全,错误的解析也全。

嗯 非常感谢!

question is not very clear

问题已经解决,谢谢。

Remove the Core and re add in ISE

只是在ISE下编译网表,IP核的ngc文件是在生产FIFO的时候生成的,没有问题,问题现在已经解决,不过同样感谢。