IIC 协议问题

在用FPGA给一个image sensor打数据,时序是和IIC差不多的,打出去的波形是正确的,示波器和signaltap均验证了,但是sensor返回ACK的时候SDA不能正常拉低,请问各位大神知道为什么吗?有遇到类似问题的吗?

signaltap 波形

你在sensor回ack的时候你的data释放了吗,也就是是高阻态吗?

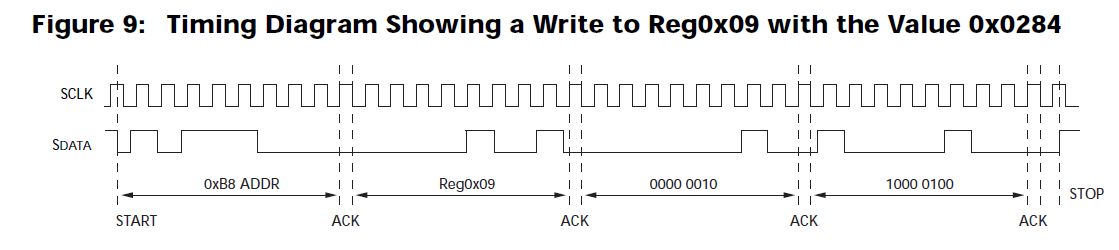

最好示波器截个图看看,截个fig9的波形

我添加了一个波形图,sda打入的是8位数据,start后,第九个scl周期进入ack状态,sdata_link为1代表sda为输出,sdata_link为0代表sda为高阻。1.检查逻辑,确定逻辑正常;

2.用示波器量FPGA近端波形,时钟与数据关系;

3.以上两点正常就是时序不满足导致;采样约束到IOB寄存器上,约束offsetin和 offsetout

逻辑应该是正确的,也用示波器看过数据和时钟,都没有问题,sensor的datasheet里面也没有提到时序约束的问题,你说的第三点能具体一点吗,不是很明白。你这个是restart吗,前面没有stop的。你第8个bit是1,难道是读的意思?其他从你的signaltap,没看别的问题

I2c 协议是支持NACK返回的 当slave没有ready的时候返回nack表示当前要读的数据没有准备好

你可以试一下:1 连续读两次相同的地址,给slave准备数据的时间。

2 换个地址读一下 可能你所读的地址是不存在的呢

3 你给出的波形不是很全,之前有没有把寄存器的地址写进去呢? i2c需要先把寄存器的地址通过写操作写入到芯片里面,然后再restart发起一个读操作。

你做功能仿真了吗?如果还是这样说明你的时序有问题。若功能仿真正常,有可能是硬件问题。因为我之前遇到过类似的问题,就是ack时SDA状态不是高阻(是在写完数据后的最后一个ack响应时,其他的ack响应都正常),重看了器件的datasheet发现该器件需要负的电压供电,改完后就正常了。如果确认逻辑功能没问题,那就看一下外接的上拉电阻有没有接对

LZ情况不明,说一下自己碰到的!

之前用了两个FPGA模拟芯片功能,一个从,一个主,一切功能波形正确,死活通讯不了!

后来乱弄了一下,发现仅同GND不行,同VDD后就可以了,虽然电平是一样的!

解决是解决了,还是没搞懂!另外,sda的输出应为:当输出数据为低电平时,正常输出,当输出数据为高电平时,sda变为高阻,高电平由上拉电阻实现。

不是restart,前面有stop的状态,根据datasheet里面给的时序来打的数据,第一个打的是0xb8,第九个周期应该是ACK,但是没有拉低sda。

我这里只是写的写操作,并没有读操作,根据给出的时序来写的,但是每写八位数据,应该返回一个ack,把sda拉低,实践并没有拉低。我更新了下波形图。

我遇到的问题就是ACK的时候sda不能被拉低。设置了三态门。