xilinx V6板子输出信号过冲是什么原因

时间:10-02

整理:3721RD

点击:

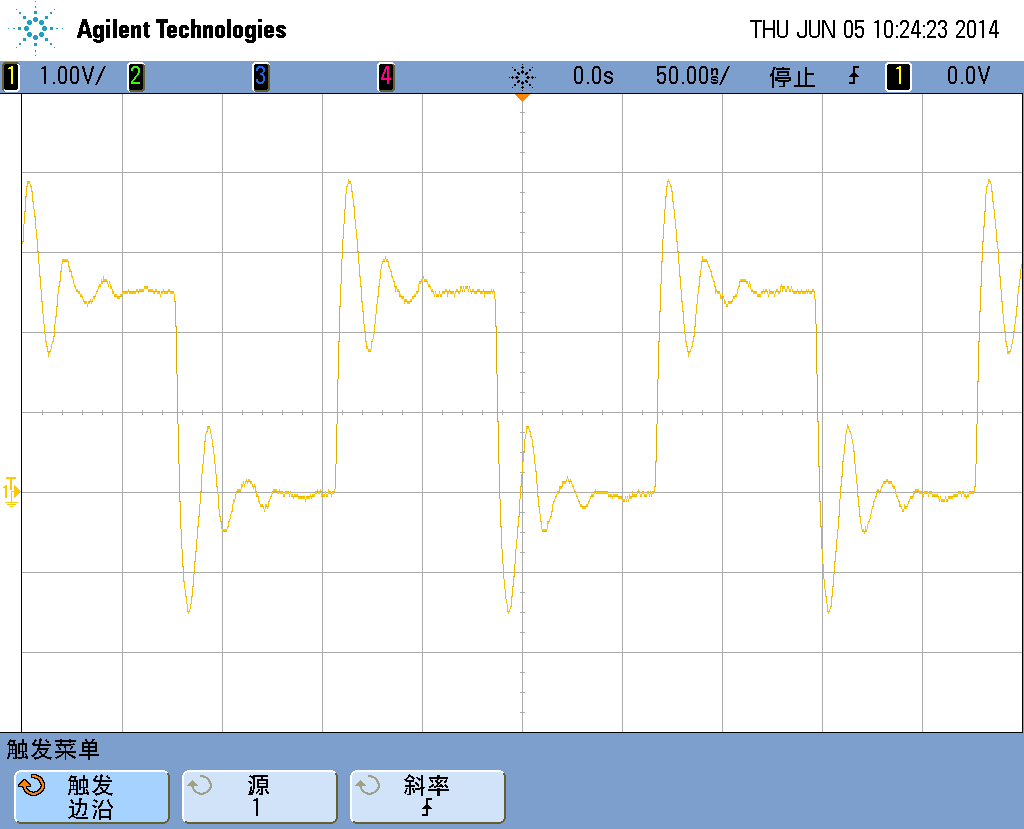

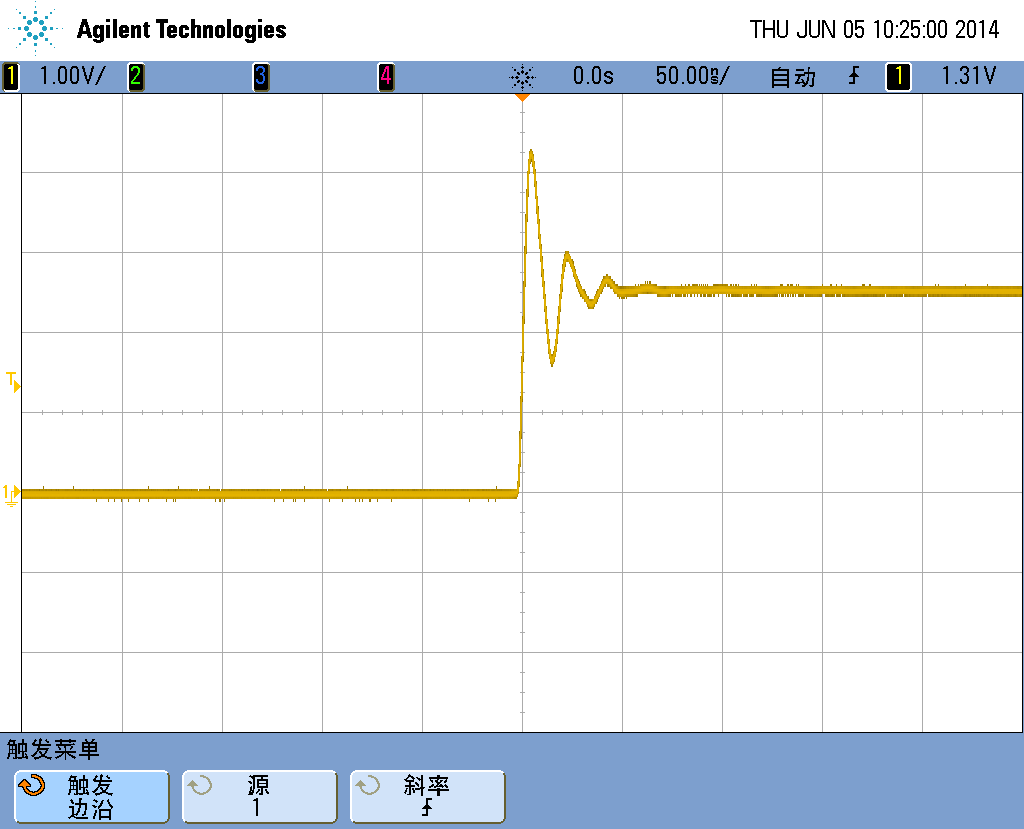

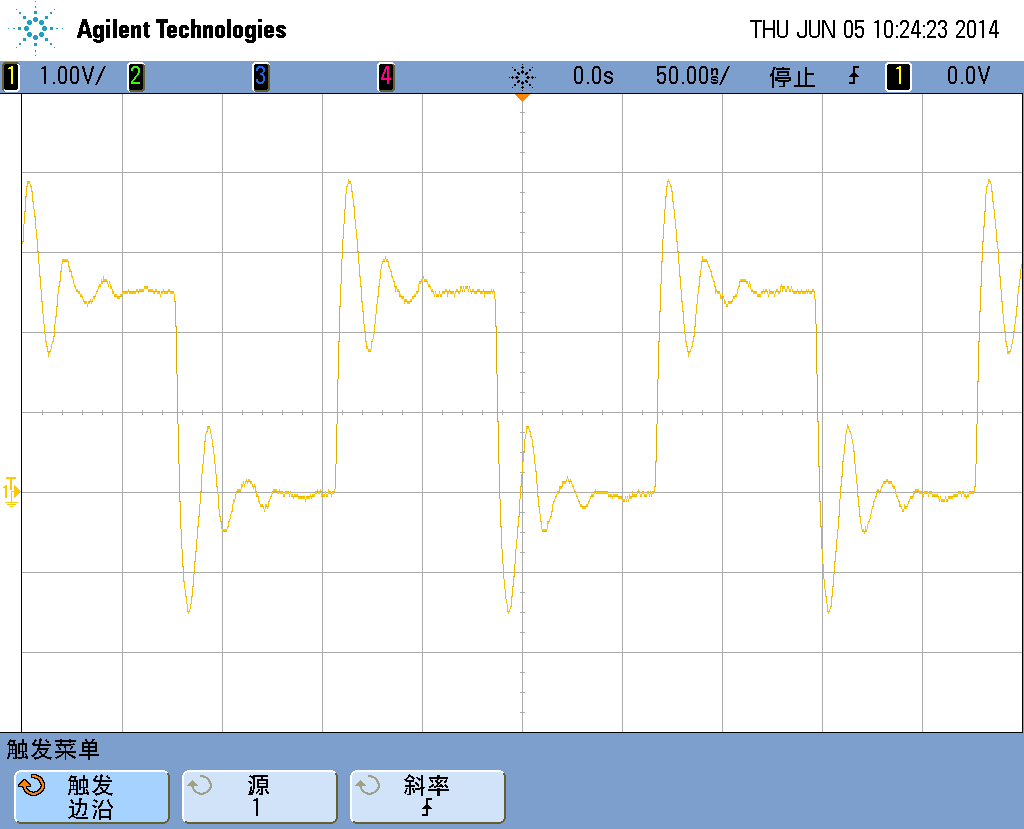

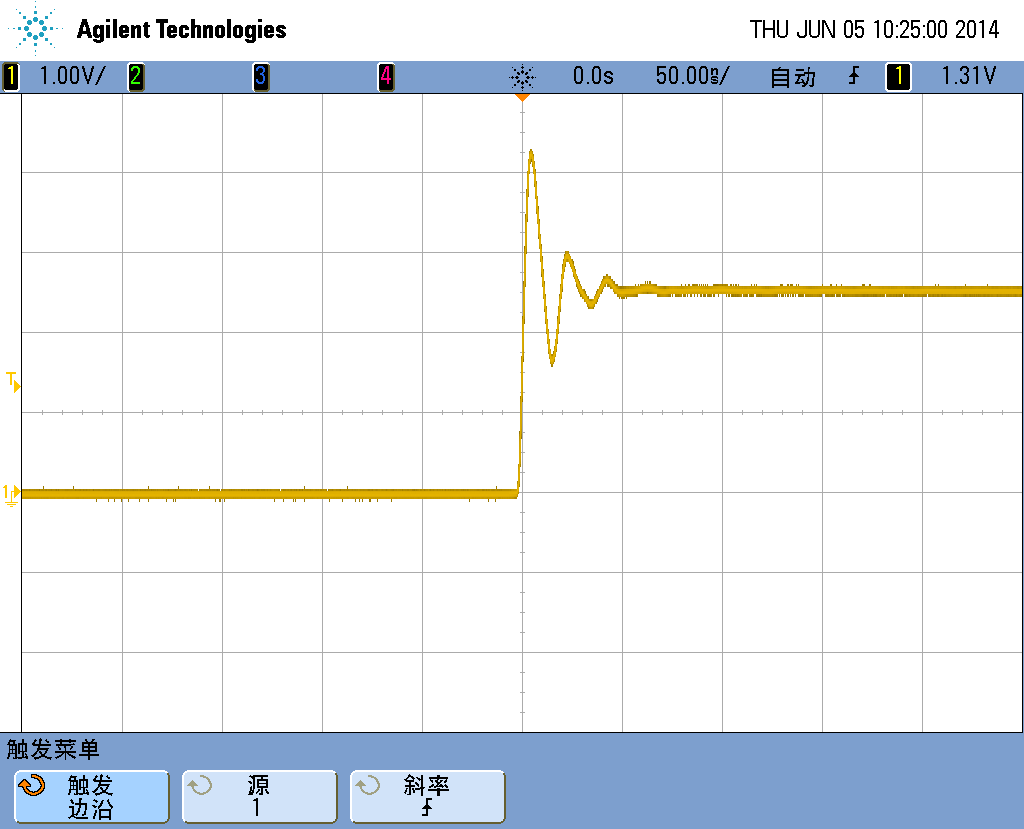

在FPGA中输出的信号出现低于Ground和高于VCC的抖动,而且输出信号频率越高抖动越大,当输出50MHz的信号时,波形就变成相当差。并且Ground和Power也受到不小的影响。如何消除这种干扰,输出干净的波形?

DCI设了没?最后一级输出是不是寄存器输出,且锁定在IOB上?

反射导致的吧 串个电阻和电容

最后一级是寄存器输出,综合时自动插了IO Buffer。 DCI是什么?IOB又是什么意思?

肯定是硬件问题,如果输入的信号正常,不可能出现怎样的问题

输出电流过大了,可以减小输出电流的驱动强度,或者在传输线上加电阻