求助!modelsim仿真没有输出

时间:10-02

整理:3721RD

点击:

用的就是论坛里的M序列发生器

library ieee;

use ieee.std_logic_1164.all;

entity pps4 is

port( clk : in std_logic;

load : in std_logic;

q : out std_logic );

end pps4;

architecture behave of pps4 is

signal c0,c1,c2,c3 : std_logic;

begin

process(clk,load)

begin

if clk'event and clk='1' then

if(load='1') then

c0<='1';

c1<='0';

c2<='0';

c3<='0';

q<=c3;

else

c1<=c0;

c2<=c1;

c3<=c2;

c0<=c3 xor c0;

q<=c3;

end if;

end if;

end process;

end behave;

testbench文件用的quartus自己生成然后改的

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY pps4_tb IS

END pps4_tb;

ARCHITECTURE ps4_arch OF pps4_tb IS

-- constants

-- signals

SIGNAL clk : STD_LOGIC;

SIGNAL load : STD_LOGIC;

SIGNAL q : STD_LOGIC;

COMPONENT pps4

PORT (

clk : IN STD_LOGIC:='1';

load : IN STD_LOGIC:='1';

q : OUT STD_LOGIC:='1'

);

END COMPONENT;

constant clk_period :time :=20 ns;

BEGIN

i1 : pps4

PORT MAP (

-- list connections between master ports and signals

clk => clk,

load => load,

q => q

);

init : PROCESS

-- variable declarations

BEGIN

wait for 20 ns;

load<='0';

wait for 2000 ns; -- code that executes only once

WAIT;

END PROCESS init;

always : PROCESS

-- optional sensitivity list

-- ( )

-- variable declarations

BEGIN

clk<='0';

wait for clk_period/2;

clk<='1';

wait for clk_period/2; -- code executes for every event on sensitivity list

END PROCESS always;

END ps4_arch;

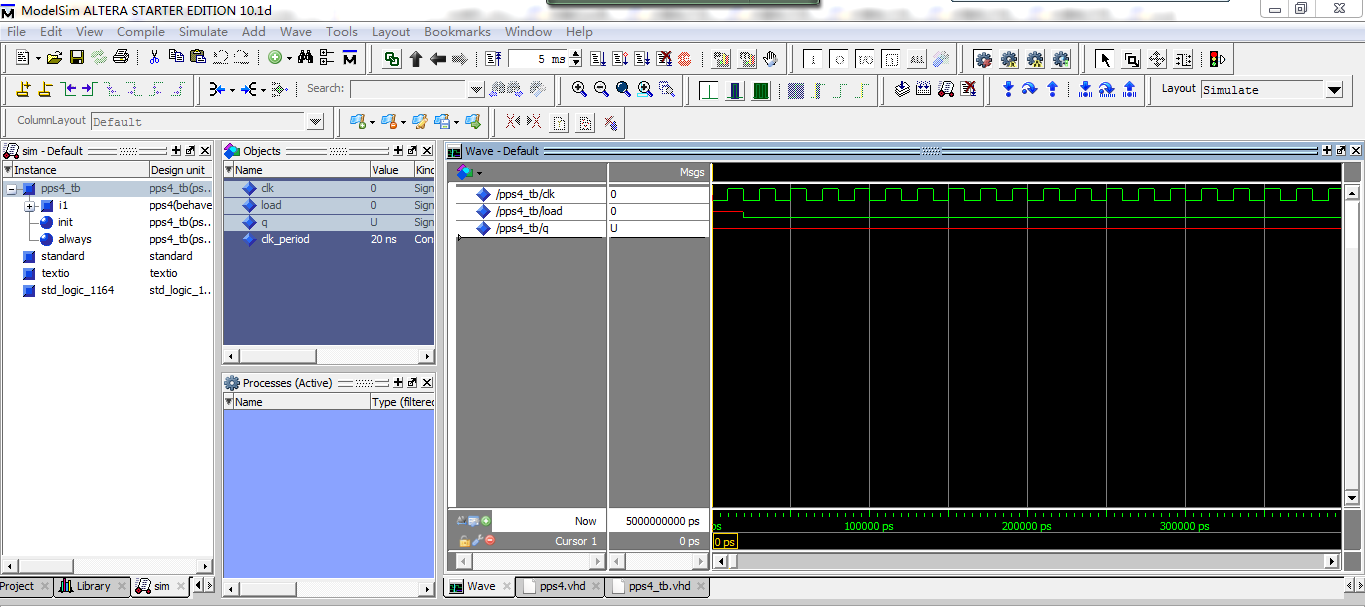

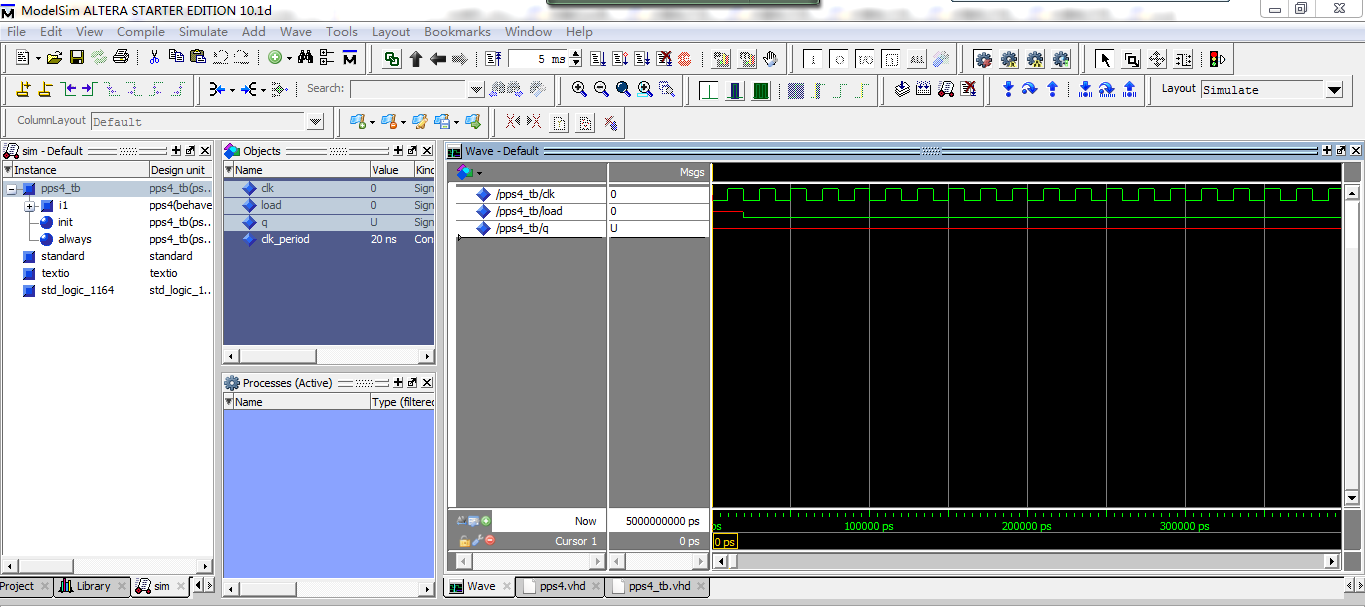

仿真以后输出只有一条红线,不知道怎么回事啊,新手求助啊。

library ieee;

use ieee.std_logic_1164.all;

entity pps4 is

port( clk : in std_logic;

load : in std_logic;

q : out std_logic );

end pps4;

architecture behave of pps4 is

signal c0,c1,c2,c3 : std_logic;

begin

process(clk,load)

begin

if clk'event and clk='1' then

if(load='1') then

c0<='1';

c1<='0';

c2<='0';

c3<='0';

q<=c3;

else

c1<=c0;

c2<=c1;

c3<=c2;

c0<=c3 xor c0;

q<=c3;

end if;

end if;

end process;

end behave;

testbench文件用的quartus自己生成然后改的

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY pps4_tb IS

END pps4_tb;

ARCHITECTURE ps4_arch OF pps4_tb IS

-- constants

-- signals

SIGNAL clk : STD_LOGIC;

SIGNAL load : STD_LOGIC;

SIGNAL q : STD_LOGIC;

COMPONENT pps4

PORT (

clk : IN STD_LOGIC:='1';

load : IN STD_LOGIC:='1';

q : OUT STD_LOGIC:='1'

);

END COMPONENT;

constant clk_period :time :=20 ns;

BEGIN

i1 : pps4

PORT MAP (

-- list connections between master ports and signals

clk => clk,

load => load,

q => q

);

init : PROCESS

-- variable declarations

BEGIN

wait for 20 ns;

load<='0';

wait for 2000 ns; -- code that executes only once

WAIT;

END PROCESS init;

always : PROCESS

-- optional sensitivity list

-- ( )

-- variable declarations

BEGIN

clk<='0';

wait for clk_period/2;

clk<='1';

wait for clk_period/2; -- code executes for every event on sensitivity list

END PROCESS always;

END ps4_arch;

仿真以后输出只有一条红线,不知道怎么回事啊,新手求助啊。

load 在 testbench 中 先设置 为 1 超过 一个 时钟 周期 然后 在 为 0

tb里面,load信号没有给初始值,从来没有出现高电平。你的代码里面,load信号做置位就没成功,导致数据全是X,

SIGNAL load : STD_LOGIC:=‘1’;

非常感谢!终于出东西了~

可以买本modelsim的书