Modelsim10.0c后仿真问题

时间:10-02

整理:3721RD

点击:

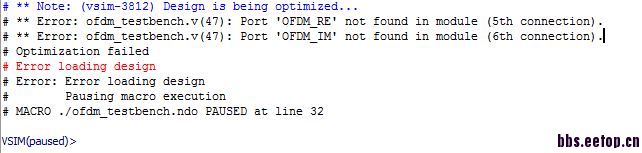

用ISE13.1调用modelsim10.0c进行implement后仿真出现问题如下:

# ** Note: (vsim-3812) Design is being optimized...

# ** Error: ofdm_testbench.v(47): Port 'OFDM_RE' not found in module (5th connection).

# ** Error: ofdm_testbench.v(47): Port 'OFDM_IM' not found in module (6th connection).

# Optimization failed

# Error loading design

# Error: Error loading design

# Pausing macro execution

# MACRO ./ofdm_testbench.ndo PAUSED at line 32

但是检查testbench module的例化是对的,有这两个端口,不知道是什么原因,哪位有经验的前辈或朋友帮忙解答下,多谢!

# ** Note: (vsim-3812) Design is being optimized...

# ** Error: ofdm_testbench.v(47): Port 'OFDM_RE' not found in module (5th connection).

# ** Error: ofdm_testbench.v(47): Port 'OFDM_IM' not found in module (6th connection).

# Optimization failed

# Error loading design

# Error: Error loading design

# Pausing macro execution

# MACRO ./ofdm_testbench.ndo PAUSED at line 32

但是检查testbench module的例化是对的,有这两个端口,不知道是什么原因,哪位有经验的前辈或朋友帮忙解答下,多谢!

功能仿真和网表仿真的对象已经不同了,你要先确定RTL代码顶层的接口和综合后的网表顶层的接口是否一致,而不是看你testbench例化的,例化的地方有,实际的可能已经没有了,我感觉工具不会乱报的,可能你的网表中确实没有这两个端口了,请在仔细检查一下。

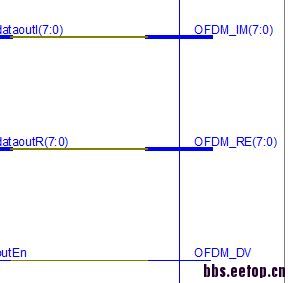

检查了,网表有这俩个信号

模块名和模块的层次结构是否发生改变,,如果是内部的连线,位宽好像是一位的,这个你要看下你的网表(代码)。

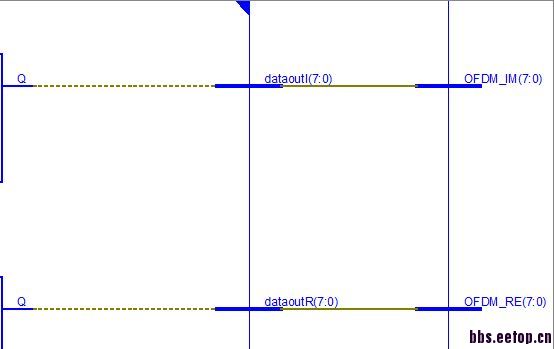

我有仔细看生成的RTL网表,信号连线都是对的,但是这两个信号是虚线,是这里的问题吗?为什么会是虚线?

这两个是顶层接口还是内部接口?

是顶层的两个输出端口

查看你综合时的报告,貌似这个地方的信号没有实际的连接属性

是综合时console里面的报告吗?有一堆warnings,但是好像无关紧要的。

还是把引用那块的代码贴出来看看吧。

应该是testbench调用被仿真文件出现了错误

test dut(a,b,c)这样是可以的

不要用类似这样的调用方法test dut(.d(a),.e(b),.f(c))

顶一个