求助:关于VHDL代码和signal tap抓波形不一致问题

时间:10-02

整理:3721RD

点击:

process(rstn,clk25m)

begin

if rstn='0' then

d1<='0';

d2<='0';

elsif clk25m'event and clk25m='1' then

d2<=d1;

d1<=SCK;

end if;

end process;

process(rstn,clk25m)

begin

if rstn='0' then

SCS_N<='1';

testdata<=(others=>'0');

elsif clk25m'event and clk25m='1' then

if d1='1' and d2='0' then

SCS_N<= SCS;

testdata<=testdata+1;

end if;

end if;

end process;

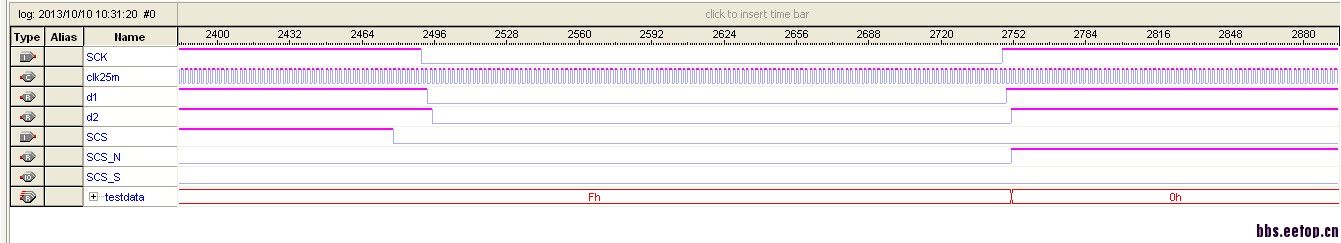

写了上面一段代码,将SCK(大概1M)同步到clk25m上来,再在clk25m时钟驱动,if d1='1' and d2='0' then条件下进行SCS到SCS_N的传输,结果用signal tap抓波形看到SCS和SCS_N的波形是相反的,望大神帮我解下惑?谢谢了。

begin

if rstn='0' then

d1<='0';

d2<='0';

elsif clk25m'event and clk25m='1' then

d2<=d1;

d1<=SCK;

end if;

end process;

process(rstn,clk25m)

begin

if rstn='0' then

SCS_N<='1';

testdata<=(others=>'0');

elsif clk25m'event and clk25m='1' then

if d1='1' and d2='0' then

SCS_N<= SCS;

testdata<=testdata+1;

end if;

end if;

end process;

写了上面一段代码,将SCK(大概1M)同步到clk25m上来,再在clk25m时钟驱动,if d1='1' and d2='0' then条件下进行SCS到SCS_N的传输,结果用signal tap抓波形看到SCS和SCS_N的波形是相反的,望大神帮我解下惑?谢谢了。

非常不錯的資料,感謝樓主熱心分享。非常不錯的資料,感謝樓主熱心分享。非常不錯的資料,感謝樓主熱心分享。