路径延迟问题

时间:10-02

整理:3721RD

点击:

在设计中碰到了这么三个错误:

三个相似,其中slack最大的如下:

Timing constraint: TS_u_clk_gen_gclk2_bufg = PERIOD TIMEGRP "u_clk_gen_gclk2_bufg" TS_CLK_200MHz_p * 0.625 HIGH 50%;

For more information, see Period Analysis in the Timing Closure User Guide (UG612).

13506306 paths analyzed, 1974 endpoints analyzed, 31 failing endpoints

31 timing errors detected. (31 setup errors, 0 hold errors, 0 component switching limit errors)

Minimum period is 8.816ns.

--------------------------------------------------------------------------------

Paths for end point u_ethernet/u_frame_gen/ip_head_data_77 (SLICE_X11Y30.C3), 297000 paths

--------------------------------------------------------------------------------

Slack (setup path): -0.816ns (requirement - (data path - clock path skew + uncertainty))

Source: u_ethernet/u_frame_gen/ipIdentifier_r_3 (FF)

Destination: u_ethernet/u_frame_gen/ip_head_data_77 (FF)

Requirement: 8.000ns

Data Path Delay: 8.682ns (Levels of Logic = 13)

Clock Path Skew: -0.002ns (0.243 - 0.245)

Source Clock: clk_125MHz rising at 0.000ns

Destination Clock: clk_125MHz rising at 8.000ns

Clock Uncertainty: 0.132ns

Clock Uncertainty: 0.132ns ((TSJ^2 + DJ^2)^1/2) / 2 + PE

Total System Jitter (TSJ): 0.070ns

Discrete Jitter (DJ): 0.254ns

Phase Error (PE): 0.000ns

通过我的分析,我认为,源寄存器ipIdentifiter_r[3]--> 目的寄存器ip_head_data[77],路径延迟为8.682ns,加上建立时间等,总共8.816ns,这都超过了系统时钟8.00ns的要求。 以至于报错!

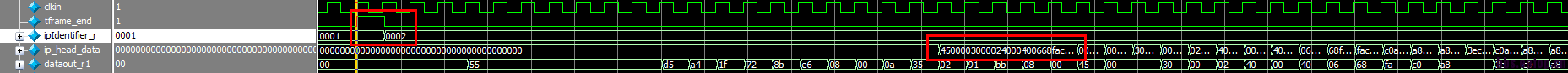

情况如下:仿真如下图:

tframe_end是在每发送一帧后使能标志帧结束。部分代码如下:

tframe_end是在每发送一帧后使能标志帧结束。部分代码如下:reg [15:0] rxIpTotalLen_r;

always @(posedge clkin)

if(reset_n==1'b0)

ipIdentifier_r <= `UD 16'd1;

else if(tframe_end==1'b1)

ipIdentifier_r <= `UD ipIdentifier_r + 1;

assign Identifier = ipIdentifier_r;

wire [159:0] ip_head_data_w1;

assign ip_head_data_w1 = {Version[3:0],HeadLen[3:0],ServiceType[7:0],TotalLen[15:0],

Identifier[15:0],Flags[2:0],FragOffset[12:0],

TimeToLive[7:0],Protocol[7:0],IpHeadChecksum[15:0],

cap_ip[31:0],pc_ip[31:0]};

always @(posedge clkin)

if(head_flag==1'b1) begin

if(cnt_base[3]==1)

ip_head_data[159:0] <= `UD ip_head_data_w1;

end

else begin

ip_head_data[159:8] <=`UD ip_head_data[151:0];

ip_head_data[7:0] <= `UD 8'h00;

end

ipIdentifiter_r 是在每发一帧结束后,自己累加1.而到达目的寄存器ip_head_data是在帧格式打包的中部组帧, 以至于相当于中间应该有很多节点,而这段时间远远超过1个时钟的周期,为什么这里还报错呢?请教各位,有什么建议,可以说一下,先谢谢了,

如果数据经过多个周期才使用,可以设置成多周期的约束。

贴的代码看不出什么东东

看的太累,打几拍吧

如果正如你所想的 数据的重组需要大于一个周期 那你就设置多周期路径,不然你优化一下在数据中间多打几拍