计数器在程序初始阶段就+1,究竟是什么原因呢

时间:10-02

整理:3721RD

点击:

本人编写的一个fpga发送预定频宽的高电平,当数据准备完毕data_ready=1,模块使能信号shitong_EN=1,之后,发出shitong_sig 信号脉冲,即shitong_sig 信号置1,同时计数器cnt0开始计数,当计数值到达指定的PW0时,shitong_sig 就清零,从而能够发出一个指定宽度的脉冲。程序代码如下:

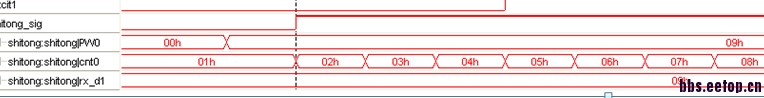

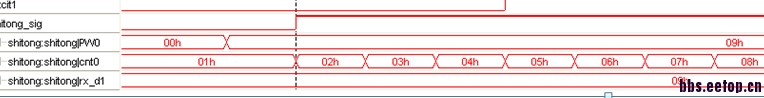

但是我在用逻辑分析仪时,发现程序一运行,cnt0 自动+1了,如图:

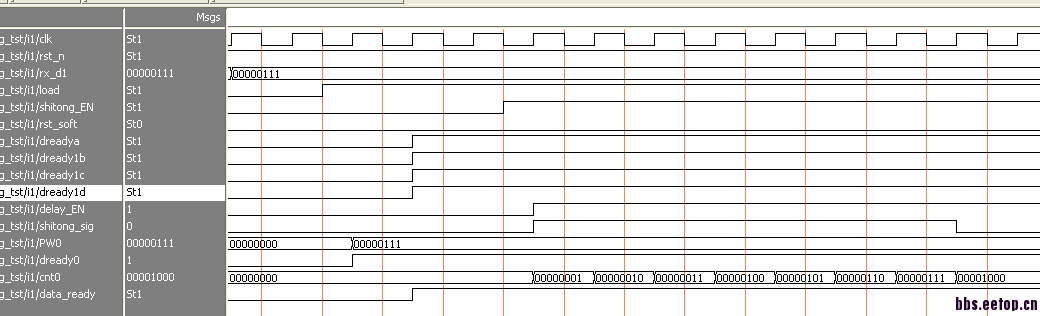

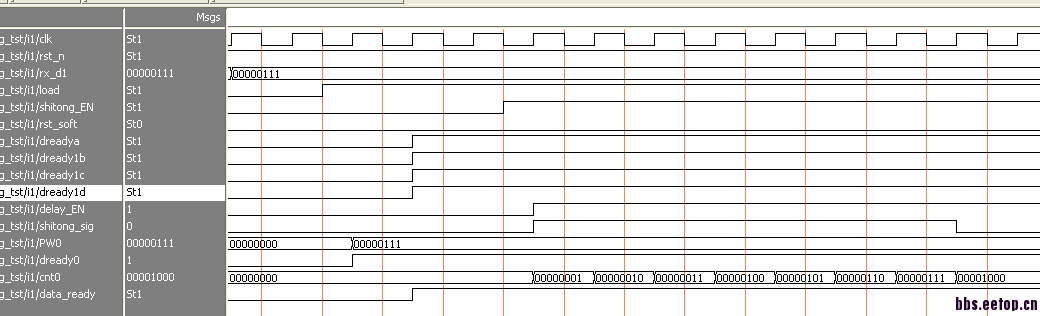

而在modelsim功能仿真时没有出现这个情况,

而在modelsim功能仿真时没有出现这个情况,

求大神指点迷津啊。

求大神指点迷津啊。

- always @ (posedge clk or negedge rst_n) begin

- if(!rst_n) begin

- cnt0 <= 8'b0;

- shitong_sig<= 1'b0;

- delay_EN<= 1'b0;

- end

- else begin

- if (rst_soft) begin

- cnt0 <= 8'b0;

- shitong_sig<= 1'b0;

- delay_EN<= 1'b0;

- end

- else begin

- if(data_ready) begin

- if(shitong_EN) begin

- if(cnt0 < PW0) begin//一旦全局使能开始,数据准备完毕,开始发波

- shitong_sig <= 1'b1;

- delay_EN <= 1'b1;

- cnt0 <= cnt0+1'b1;

- end

- if(cnt0 == PW0[7:0]) begin

- shitong_sig<= 1'b0;

- cnt0<=cnt0+1'b1;

- delay_EN <= 1'b1;

- end

- if(cnt0 > PW0[7:0]) begin

- shitong_sig<= 1'b0;

- delay_EN <= 1'b1;

- cnt0<=cnt0;

- end

- end

- end

- end

- end

- end

- endmodule//08.16

但是我在用逻辑分析仪时,发现程序一运行,cnt0 自动+1了,如图:

而在modelsim功能仿真时没有出现这个情况,

而在modelsim功能仿真时没有出现这个情况, 求大神指点迷津啊。

求大神指点迷津啊。

明显PW0信号变化导致cnt动作了

在modelsim里面是正常的,PW0达到预定值,信号跳变,可是在板调试时,也就是用signaltap ii 调试时,PW0还是0的时候,使能也为0 他就自动+1了,这不干PW0的事儿啊

注意看signaltapII 的仿真结果图,PW0还没跳变之前,cnt0就已经是1了,百思不得其解啊

找到原因了,原来是我在modelsim之后新加的模块导致的,我来改改试试看,坑爹啊

复位信号处理的很怪异。