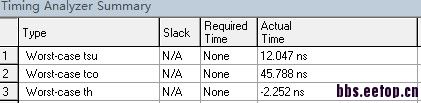

不明白的Worst-case th

,这个负值说明什么问题,在什么情况下才会是负值,什么情况下才会是正负?

,这个负值说明什么问题,在什么情况下才会是负值,什么情况下才会是正负?

worst case th应该是hold吧

required time是None,说明你并没有做约束,因此slack也是N/A

hold time为负值并没有问题,你看到的教科书中hold是指时钟沿之后数据需要稳定的时间。

事实上,教科书上只是在分析一个DFF。

假如分析的cell是一个比较复杂的组合+时序逻辑,cell的某一个数据端口是D,某一个时钟端口是CK

1. 如果D和CK在cell内部没有经过延时直接连接到某个DFF,那么这个cell上D相对于CK的setup/hold time跟传统教科书上是一致的,假设setup是0.1ns,hold是0.2ns。

2. 如果CK在cell内部直接连接到某一个DFF,而D经过一堆的复杂组合逻辑,延时是1ns,那么从该cell的端口来看,setup的要求是0.1+1, hold要求是0.2-1=-0.8

3. 如果D在cell内部直接连接到某一个DFF,而CK经过几级buf延时了0.5ns才到达DFF,那么从cell的端口来看,setup的要求是0.1-0.5=-0.4,hold要求是0.2+0.5=0.7ns。

上面第二种情况就是负的hold,对应到altera的LE上,可能就会出现负的hold

在你举的这3点中,第三点的保持时间依然可以指在时钟沿到达cell之后需要保持的时间,但第二点我尝试着还用这个理论来解释,却怎么也解释不不合理,因为在第二点中,需要过了1.1ns的建立时间后时钟沿才到达cell,那么还用这个理论来解释的话,我认为保持时间应该还是0.2ns才对啊?!不好意思,小弟初学,所以还不能正确理解

你理解的hold time还是针对单一的寄存器,你这样想

针对第二条:

cell内部的DFF才是hold 检查的根节点,如果想满足D在CK后面需要保持0.2ns以上,那么从cell端口上来看,只需要D在CK后面保持0.2-1 也就是如果D的变化在CK前面不超过0.8ns时,D经过1ns延时,到达寄存器端口时即可满足寄存器上数据在CK之后保持0.2ns以上。

这就是传说中的负hold time

顶下2楼。