DC能综合ISE的库么?

还有就是我这样在ISE的环境下设计芯片可行么?

这个问题想了很久了,网上也没找到合适的答案,先谢谢了!

ISE下面有对应的db格式的库文件,你可以把这个制定成DC的target library。但是对于你使用的ISE的IP的话,就不知道有没有对应的db格式的库,如果有的话直接作为DC的库就可以综合了。

我搜索了ISE下面的所有文件,发现没有.db格式的文件。不过有一些.dbs格式的文件,是这个么?

除非是软核,其它的ip asic都不能用。

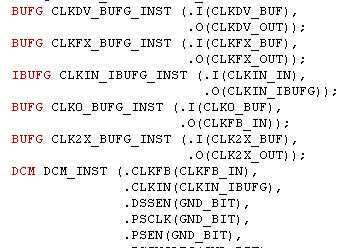

大部分用到的IP应该都是软核;就像下图所示,ISE的IP代码中通常会调用一些模块,这些模块是ISE自己定义的(就像图中的BUFG和DCM),放在ISE的库中ISE能自动识别,但DC如果没有这些库肯定是无法识别这些模块的,怎样把ISE的库添加到DC中?

好奇心害死猫啊,求大神回答!

BUFG这不是ip,是stand cell,如果你rtl一定要这样写的话(asic一般时钟留给pr处理),替换成代工厂类似的stand cell就可以了;

我觉得如果你安装linux版本的ISE,在third party tools中的synthesis工具选成DC,指定了DC的位置,Xilinx应该会直接调用~我没试过,但觉得应该是这样。不妨参考一下

楼上是正解(看你头像貌似我认识,O(∩_∩)O~);我开始的理解是fpga的rtl转asic。

这问题怎么解决啊,我也碰到相似的情况,要综合ISE下的FPGA工程,工程里有BUFG和IBUFG,高手在吗?

想都不要想,DC连SRAM这样的IP都处理不了,SRAM要用foundry的MC产生(一般小于64B,可以用DFF替代,再大不经济),8bit以上乘法器也不能使用DC,DC只能处理通用逻辑,