信号上升沿的判断d

时间:10-02

整理:3721RD

点击:

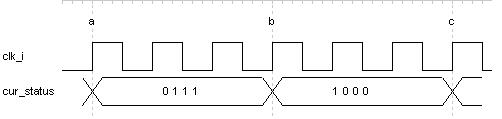

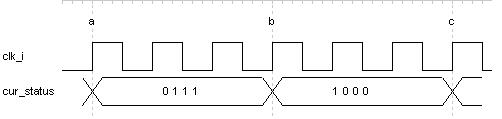

我们要对状态机信号cur_status == 4'b1000的状态进行判断;波形如下:

方案A:

assign sign1 = (cur_status==4'b1000) ? 1: 0;

always @(posedge clk_i)

sign1_delay <= sign1;

assign rise = sign1 & !sign1_delay;

方案B:

always @(posedge clk_i)

if (cur_status==4'b1000) sign1 <= 1;

else sign1 <= 0;always @(posedge clk_i)

sign1_delay <= sign1

assign rise = sign1 & !sign1_delay;

这两种方案那个好点?

就是sign1的延时是cur_status的延时加上自己的延时;这样做法会造成时序上的问题吗?

方案A:

assign sign1 = (cur_status==4'b1000) ? 1: 0;

always @(posedge clk_i)

sign1_delay <= sign1;

assign rise = sign1 & !sign1_delay;

方案B:

always @(posedge clk_i)

if (cur_status==4'b1000) sign1 <= 1;

else sign1 <= 0;always @(posedge clk_i)

sign1_delay <= sign1

assign rise = sign1 & !sign1_delay;

这两种方案那个好点?

我觉得第一种好一些,第二种应该在cur_status==4'b1000之后的第二个时钟上升沿才变为“1”,小编可以仿真下!

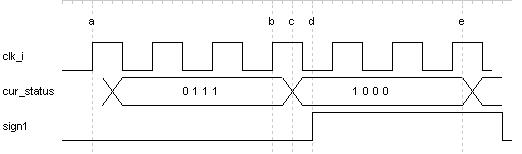

恩,方案B,信号sign1会被打上一拍,延时一个周期;但是在实际的应用中,方案A会不会有时序上的问题;例如在方案A中,实际的波形会不会如下:

就是sign1的延时是cur_status的延时加上自己的延时;这样做法会造成时序上的问题吗?

时序上要人为保证的,不过一般来说没有问题吧,就一个门而已

时序上应该不会有问题,毕竟逻辑挺简单的

呵呵,谢谢大家的回答;现在心里明白多了;多谢了

我推荐还是方案B好点。 前者状态机从4‘b0111到4’b0111转变,期间会出现毛刺, 当然如果你的时钟频率不是太快的话,两者都没有问题, 如果时钟太快了,有可能导致后面第一个时钟采样的signal1 不对, 会逐级的往后为传递。

方案B比方案A晚一个clk,其它差不多,看你的设计的时序需求了。

楼上说的问题不用担心,这个由STA保证setup/hold时间的。

另外,建议lz写数字时,总是把位宽带上,写1'b0,1'b1。

还有,assign sign1 = (cur_status==4'b1000) ? 1: 0;可以写成assign sign1 = (cur_status==4'b1000);

个人觉得这样看起来更老练。

多谢大家的教导;在这里很受学习;