求用VERILOG如何实现信号下面的功能,关于信号计数,识别的

信号输入:fop_count (当有fop时,输入脉冲宽度为20us,无fop时,输入为低电平)

时钟CLK,10MHz

信号输出:fop_out

功能实现:

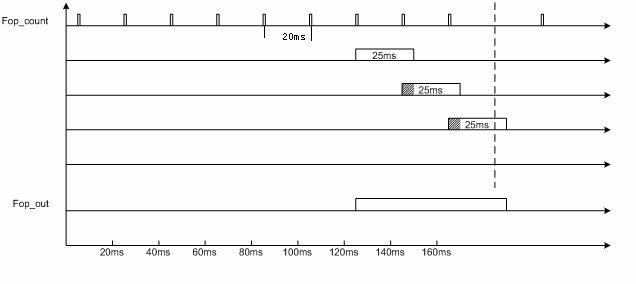

1)连续6个周波监测到FOP动作,Fop_out输出一个25ms的正脉冲,在之后的每个周波内如有FOP动作,Fop_out从该此刻起继续保持25ms的高电平。

2)在FOP动作次数累计过程中,一旦出现有一个周波内未检测到FOP动作,动作累计次数自动清零,Fop_out从上一次FOP动作开始累计输出25ms后自动拉低,等待FOP动作满足连续6个周波后再次输出。

设计思路:

1:在fop_count信号每个fop的下降沿产生25ms的高电平信号,用以检测下一个周期是否存在fop;

2:若存在,那就对检测到的fop进行计数,检测到5个fop的时候(加上之前的一个,共6个),用以输出25ms

3:6个脉冲之后一直存在fop的话,那输出信号如何实现,用不存在fop为条件做为中断条件?

求大神帮忙 具体的程序该如何实现啊?

谢谢····

时钟信号为10MHz

作业题还是自己动动脑子吧

这种事情你不花钱没人帮你哦

我的一点想法,供参考。看图fop_count应该是脉冲信号,怎么命名为计数器?

1)对fop_count上升沿采样循环计数,记作cnt6,当计数到6个时输出25ms宽脉冲fop_out;

2)对输出脉冲fop_out长度计数,记作pluse_width_cnt25ms;

3)在fop_out高电平期间,如果检测到fop_count脉冲信号,则清零pluse_width_cnt25ms;

4)如果pluse_width_cnt25ms计数到25ms时间长度,则拉低输出fop_count,并清零cnt6.

用状态机的思路写比较简单。

状态1:fop_count计数达到6,跳到下一状态

状态2:输出fop_out.计数25ms,计数到达后判断fop_count。fop_count<6,跳状态1,否则继续在状态2。25ms计数器重新计数。

另外,上面代码fop_count是独立计数的。

如果fop_count只在fop_out输出为0时计数,上面的代码也会有些不同。

功能实现:

1)连续6个周波监测到FOP动作,Fop_out输出一个25ms的正脉冲,在之后的每个周波内如有FOP动作,Fop_out从该此刻起继续保持25ms的高电平。

2)在FOP动作次数累计过程中,一旦出现有一个周波内未检测到FOP动作,动作累计次数自动清零,Fop_out从上一次FOP动作开始累计输出25ms后自动拉低,等待FOP动作满足连续6个周波后再次输出。

设计思路:

1:在fop_count信号每个fop的下降沿产生25ms的高电平信号,用以检测下一个周期是否存在fop;

2:若存在,那就对检测到的fop进行计数,检测到5个fop的时候(加上之前的一个,共6个),用以输出25ms

3:6个脉冲之后一直存在fop的话,那输出信号如何实现,用不存在fop为条件做为中断条件?

有以下疑问:

1. 连续6个周波检测到Fop动作,是指Fop_count的6个周波还是10MHz clk的6个周波?

2. 在fop_count信号每个fop的下降沿产生25ms的高电平信号,到底是Fop_count的上升沿产生25ms信号还是下降沿?