Holdtime 可以小于0么?有么有达人给我讲下

时间:10-02

整理:3721RD

点击:

刚发错版了。再发次。╮(╯▽╰)╭。如题,导师说过holdtime可能小于零,当小于零时触发器还能正常工作,到现在我还是没明白holdtime能小于零在什么情况下会出现,而且出现了为什么不会导致不定态的出现。请大家给我讲讲,求讨论,求知识。

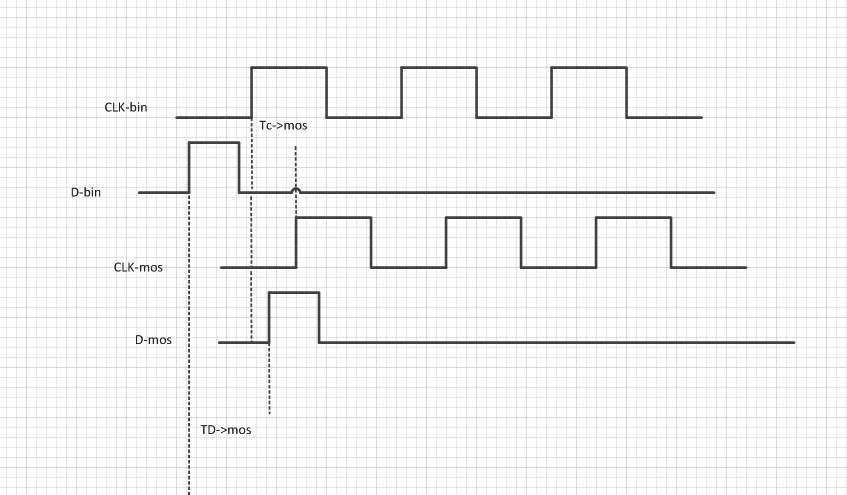

可以小于零,hold time是在FlipFlop的pin脚上量测的,如果data pin脚到MOS管的时延 - clk pin脚到器件内部MOS的时延 > 实际的hold time,那么,表现在pin脚上,hold time 就会使负的。

对的。