门控时钟与使能问题?

时间:10-02

整理:3721RD

点击:

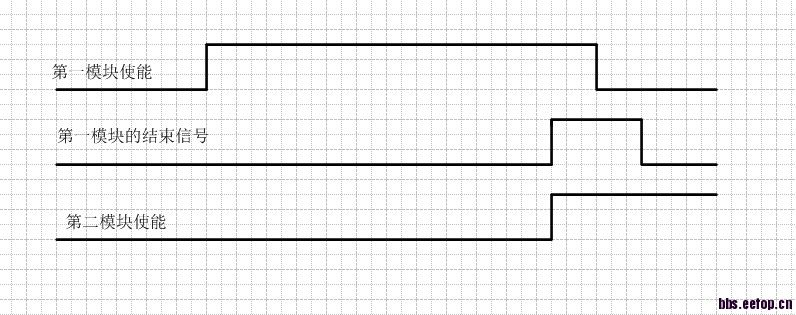

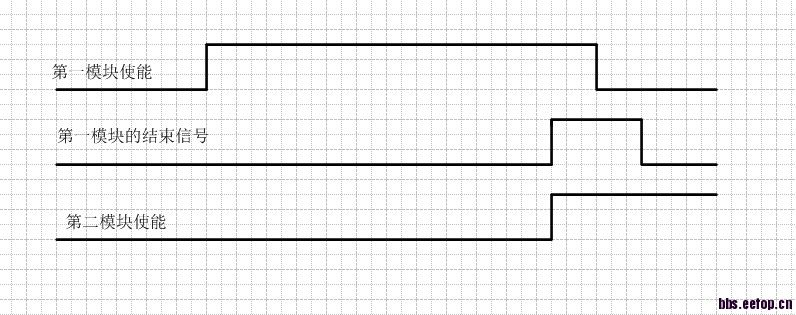

其实就是模块之间的调度问题,当第一模块工作完成后 , 使其使能拉低不工作,产生第一模块的结束信号,在下一个时钟来的时候 拉低产生的第一模块的结束信号。 第二模块检测到第一模块的结束信号后将其使能拉高开始工作。 这样的话 用DC做综合的时候 加门控时钟的话 会不会导致第一模块的结束信号无法拉底?如果不对这个信号使用门控时钟应该杂么办 有没有命令可以不对产生使能的寄存器做门控时钟?求大侠速度解决啊 很急 小弟在此先谢谢各位大侠!

主要是第一模块的结束信号是寄存器的形式 应该会导致使用门控时钟 所以后面就么办法拉低了!自己认为。

主要是第一模块的结束信号是寄存器的形式 应该会导致使用门控时钟 所以后面就么办法拉低了!自己认为。

没看明白,如果是DC自动加的时钟门控应该是不会影响你的功能

您的意思是不是只要我的代码写的功能真确,那么我用dc加门控时钟就不会对功能产生影响?主要是我的使能直接相互关联着,就像握手信号一样,这样会不会产生影响?