modelsim仿真时,clk显示nodata,求解决

时间:10-02

整理:3721RD

点击:

我用quartus2 11.0版本的创建了工程,并编写了如下的testbench:`timescale 10 ns/ 1 ps

module serial_1_vlg_tst();

// constants

// general purpose registers

reg eachvec;

// test vector input registers

reg clk;

reg key_input;

reg rst;

reg rxd;

// wires

wire [7:0] en;

wire [7:0] rxd_buf;

wire [7:0] seg_data;

wire tr;

wire txd;

// assign statements (if any)

serial_1 i1 (

// port map - connection between master ports and signals/registers

.clk(clk),

.en(en),

.key_input(key_input),

.rst(rst),

.rxd(rxd),

.rxd_buf(rxd_buf),

.seg_data(seg_data),

.tr(tr),

.txd(txd)

);

initial

begin

#20 rst=1'b1;

#20 rst=1'b0;

#20 key_input=1'b1;

#17000 key_input=1'b0;

#5 rxd= 1'b1;

repeat(100000) #2 clk=~clk;

$monitor("New txd is %d and occurs at %t",txd,$time);

$monitor("New rxd_buf is %d and occurs at %t",rxd_buf,$time);

$monitor("New en is %d and occurs at %t",en,$time);

$monitor("New seg_data is %d and occurs at %t",seg_data,$time);

// code that executes only once

// insert code here --> begin

// --> end

$display("Running testbench");

#10000;

end

always #2 clk=~clk;

always@(tr)

begin

if (tr<=0) begin

repeat(3) #10420 rxd=1'b0; //接收起始位以及数据前两个0位

repeat(2) #10420 rxd=1'b1;

#10420 rxd=1'b0; //接收到0x35

#10420 rxd=1'b1;

#10420 rxd=1'b0;

#10420 rxd=1'b1;

#10420 rxd=1'b1; //保持高位,串口停止接收

end

else begin

#5 rxd=1'bz;

end

@eachvec;

end[attach]447839[/attach]

endmodule

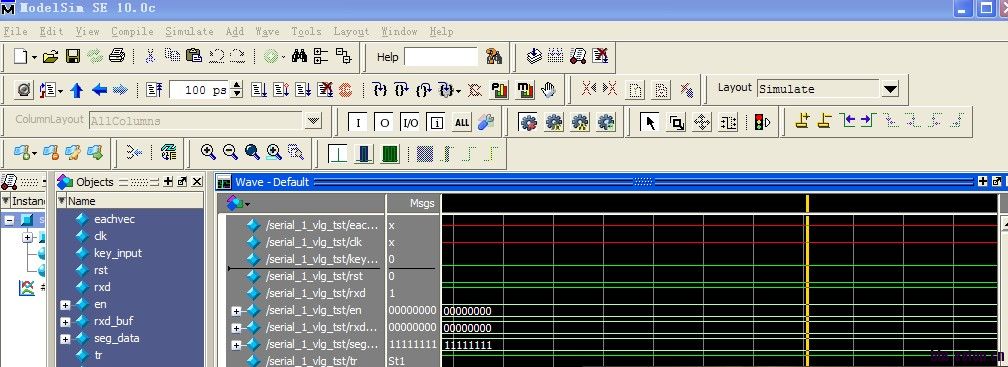

可是联合仿真之后,波形中时钟没有数据,具体可以从图中看到,其他数据有,谁能指点一下?

module serial_1_vlg_tst();

// constants

// general purpose registers

reg eachvec;

// test vector input registers

reg clk;

reg key_input;

reg rst;

reg rxd;

// wires

wire [7:0] en;

wire [7:0] rxd_buf;

wire [7:0] seg_data;

wire tr;

wire txd;

// assign statements (if any)

serial_1 i1 (

// port map - connection between master ports and signals/registers

.clk(clk),

.en(en),

.key_input(key_input),

.rst(rst),

.rxd(rxd),

.rxd_buf(rxd_buf),

.seg_data(seg_data),

.tr(tr),

.txd(txd)

);

initial

begin

#20 rst=1'b1;

#20 rst=1'b0;

#20 key_input=1'b1;

#17000 key_input=1'b0;

#5 rxd= 1'b1;

repeat(100000) #2 clk=~clk;

$monitor("New txd is %d and occurs at %t",txd,$time);

$monitor("New rxd_buf is %d and occurs at %t",rxd_buf,$time);

$monitor("New en is %d and occurs at %t",en,$time);

$monitor("New seg_data is %d and occurs at %t",seg_data,$time);

// code that executes only once

// insert code here --> begin

// --> end

$display("Running testbench");

#10000;

end

always #2 clk=~clk;

always@(tr)

begin

if (tr<=0) begin

repeat(3) #10420 rxd=1'b0; //接收起始位以及数据前两个0位

repeat(2) #10420 rxd=1'b1;

#10420 rxd=1'b0; //接收到0x35

#10420 rxd=1'b1;

#10420 rxd=1'b0;

#10420 rxd=1'b1;

#10420 rxd=1'b1; //保持高位,串口停止接收

end

else begin

#5 rxd=1'bz;

end

@eachvec;

end[attach]447839[/attach]

endmodule

可是联合仿真之后,波形中时钟没有数据,具体可以从图中看到,其他数据有,谁能指点一下?

RE: modelsim仿真时,clk显示nodata,求解决

急求解啊

加上:

initial

clk = 0;

然后再:

always #2 clk=~clk;

clk没有初始值

clk没有付初值哦。 clk = 0;